### Classes of systems/models considered in this course

- Continuous: differential equations, ... ???

- Discrete: state machines, transition systems, ...

- Timed: discrete-event, timed automata, ...

- Dataflow: process networks, SDF, ...

- Probabilistic: Markov chains, ...

3

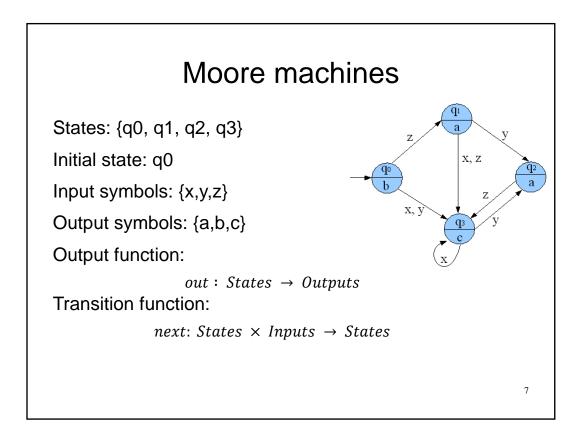

#### Finite State Machines – Formal Definition

An FSM is a tuple

$(I, O, S, s_0, \delta, \lambda)$

- *I*: set of inputs

- *O*: set of outputs

- S: set of states

- $s_0 \in S$ : initial state

- $\delta: S \times I \to S$ : transition function

- $\lambda$ : output function

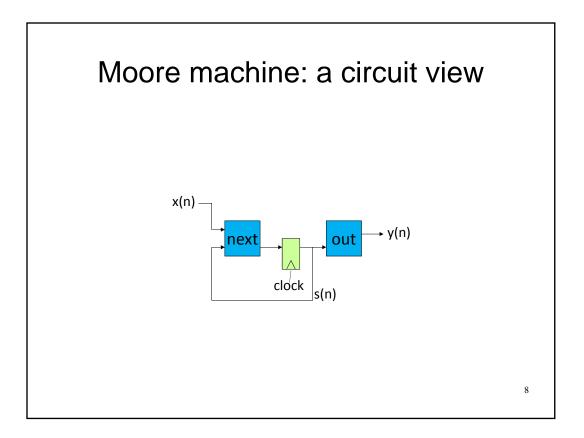

- ► If the FSM is of type **Moore**:

$\lambda:S\to O$

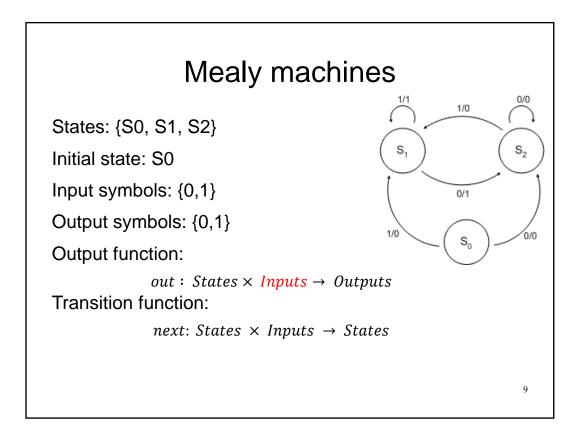

• If the FSM is of type **Mealy**:

$\lambda:S\times I\to O$

Stavros Tripakis (UC Berkeley)EE 244, Fall 2016State machines, circuits11 / 30

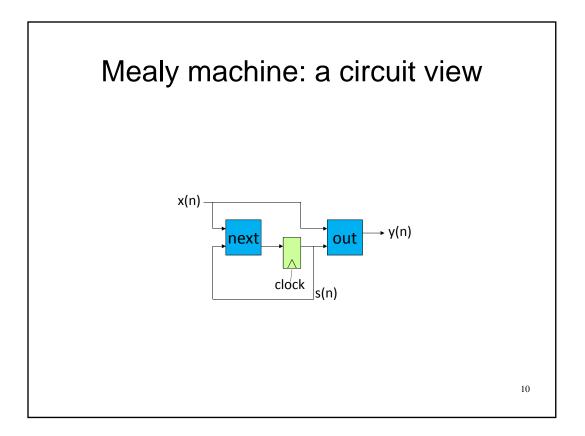

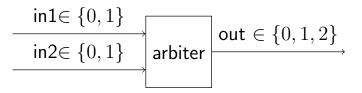

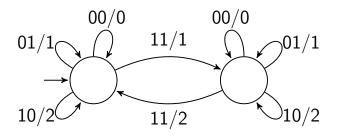

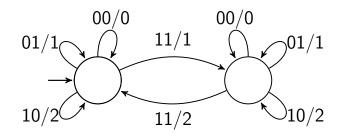

#### Example: Mealy Machine

structure:

behavior:

### CIRCUITS

Stavros Tripakis (UC Berkeley)

EE 244, Fall 2010

State machines, circuits 13 / 30

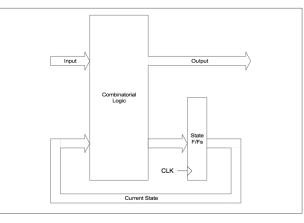

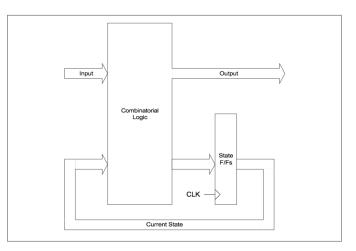

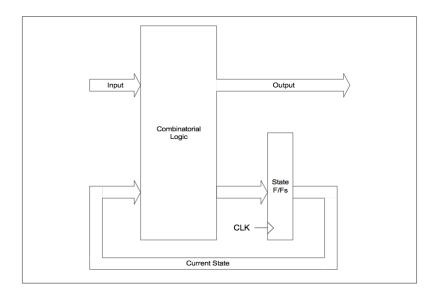

#### Synchronous Circuits – Generic structural view:

- Combinational logic part: a network of logical gates (AND, OR, NOT, XOR, ...).

- Memory/state of the circuit: some type of digital memory element (e.g., D-type flip-flop).

- Synchronous: clock arriving conceptually synchronously (simultaneously) at all flip-flops.

- Circuit: a network of connected gates and flip-flops ("netlist").

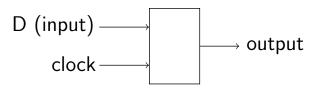

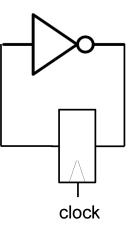

#### Memory element: D flip-flop

Behavior (simplified<sup>1</sup>):

- Clock input defines a set of times  $t_1, t_2, t_3, ...$  (e.g., up-edges of a periodic pulse).

- The value of output remains constant during the interval  $[t_k, t_{k+1})$  and equal to the value of the input D at  $t_k$ .

- "Door-opening" metaphor.

- Memory elements often have more inputs (e.g., resets to initialize state).

<sup>1</sup>More accurate description of timing behavior in timing analysis lecture. Stavros Tripakis (UC Berkeley) EE 244, Fall 2016 State machines, circuits 15 / 30

#### Is the D flip-flop a state machine?

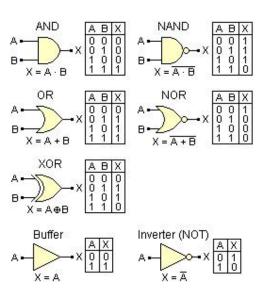

#### Combinational logic gates

Stavros Tripakis (UC Berkeley)

EE 244, Fall 20

State machines, circuits 17 / 30

#### Are logic gates state machines?

# Digital Circuits: Networks of Flip-Flops and Logic Gates

For now, we consider **acyclic** circuits: they **can** have feedback, but any feedback loops are "broken" by flip-flops:

Are the dynamics of such circuits well-defined? How?

```

Stavros Tripakis (UC Berkeley)EE 244, Fall 2016State machines, circuits19 / 30

```

From Circuits to State Machines

Is this a state machine?

#### From Circuits to State Machines

Is this a state machine? Is it a Mealy or Moore machine? How are  $(I, O, S, s_0, \delta, \lambda)$  defined? What would a Moore Machine look like?

```

Stavros Tripakis (UC Berkeley)

EE 244, Fall 2016

State machines, circuits

21 / 30

```

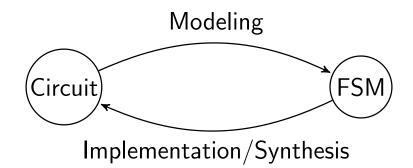

#### State Machines and Synchronous Circuits

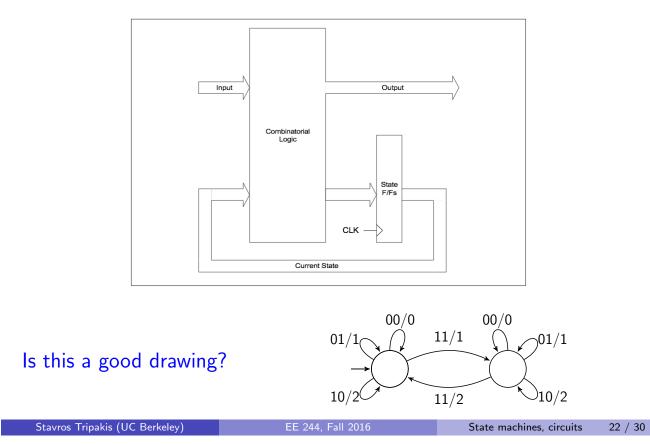

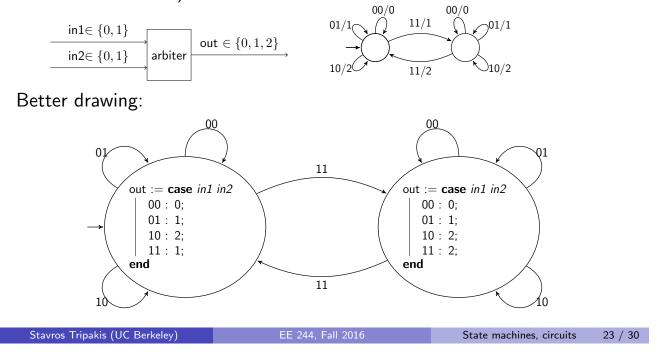

#### Drawing Mealy Machines Correctly

Traditional drawing mixes transition and output functions, although these are independent (this matters in the case of circuits, for instance, where outputs might change multiple times before stabilizing - c.f. discussion on circuits that follows):

#### Modeling and Implementation/Synthesis

What we have done / what we will do next:

#### From FSMs to Circuits

"Brute-force" implementation:

- $\log n$  flip-flops, where n = |S| = number of states of the FSM.

- $\log k$  input wires, where k = |I| = number of input symbols.

- $\log m$  output wires, where m = |O| = number of output symbols.

- Multiplexers to implement transition and output functions.

More efficient implementations: the **logic synthesis** problem. Several subproblems:

- State encoding (or *state assignment*)

- Logic minimization

- ...

#### Stavros Tripakis (UC Berkeley)

EE 244, Fall 2016

State machines, circuits 25 / 30

#### From FSMs to Circuits

Let's implement this FSM (on whiteboard):

#### From FSMs to Circuits

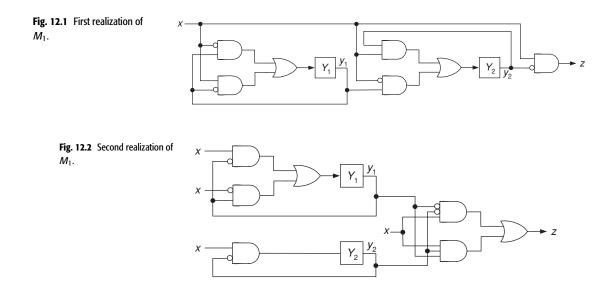

Several combinatorial optimization problems.

E.g., *state assignment* (state encoding): how to encode the states of a given FSM as boolean vectors. Which of the many possible encodings to choose?

Example (taken from [Kohavi, 1978]):

| Table 12.1         Machine M1 |       |       |       |       |  |  |  |  |  |

|-------------------------------|-------|-------|-------|-------|--|--|--|--|--|

|                               | 1     | V S   | z     |       |  |  |  |  |  |

| P S                           | x = 0 | x = 1 | x = 0 | x = 1 |  |  |  |  |  |

| A                             | Α     | D     | 0     | 1     |  |  |  |  |  |

| В                             | Α     | С     | 0     | 0     |  |  |  |  |  |

| С                             | С     | В     | 0     | 0     |  |  |  |  |  |

| D                             | С     | Α     | 0     | 1     |  |  |  |  |  |

|   |                                             | $Y_1 Y_2$ |       | z     |       |

|---|---------------------------------------------|-----------|-------|-------|-------|

|   | <i>y</i> <sub>1</sub> <i>y</i> <sub>2</sub> | x = 0     | x = 1 | x = 0 | x = 1 |

| A | 00                                          | 00        | 10    | 0     | 1     |

| В | 01                                          | 00        | 11    | 0     | 0     |

| С | 11                                          | 11        | 01    | 0     | 0     |

| D | 10                                          | 11        | 00    | 0     | 1     |

|   |                                             |           |       |       |       |

(a) Assignment  $\alpha$

|   |                                             | $Y_1 Y_2$        |       | Z     |       |

|---|---------------------------------------------|------------------|-------|-------|-------|

|   | <i>y</i> <sub>1</sub> <i>y</i> <sub>2</sub> | $\overline{x=0}$ | x = 1 | x = 0 | x = 1 |

| A | 00                                          | 00               | 11    | 0     | 1     |

| В | 01                                          | 00               | 10    | 0     | 0     |

| С | 10                                          | 10               | 01    | 0     | 0     |

| D | 11                                          | 10               | 00    | 0     | 1     |

(b) Assignment  $\beta$

Stavros Tripakis (UC Berkeley)

EE 244, Fall 2016

State machines, circuits 27 / 30

#### From FSMs to Circuits

The two state encodings result in two very different circuits:

Figures taken from [Kohavi, 1978].

# An elegant notation for (not necessarily finite) state machines: Lustre

A program in the synchronous language Lustre [Halbwachs et al., 1991]:

node Edge (X : bool) returns (E : bool); let E = false -> X and not pre X ; tel

Can you guess its meaning?

$E_0 = false$  $E_{k+1} = X_{k+1} \land \neg X_k$

Quiz: write a counter in Lustre.

```

Stavros Tripakis (UC Berkeley)

EE 244, Fall 2016

State machines, circuits

29 / 30

```

#### Bibliography

Hachtel, G. D. and Somenzi, F. (1996).

Logic Synthesis and Verification Algorithms.

Kluwer.

Halbwachs, N., Caspi, P., Raymond, P., and Pilaud, D. (1991).

The synchronous dataflow programming language Lustre.

Proceedings of the IEEE, 79(9):1305–1320.

Hopcroft, J. E. and Ullman, J. D. (1990).

Introduction To Automata Theory, Languages, And Computation.

Addison-Wesley.

Kohavi, Z. (1978).

Switching and finite automata theory, 2nd ed. McGraw-Hill.