# Fundamental Algorithms for System Modeling, Analysis, and Optimization

### Stavros Tripakis

UC Berkeley EECS 144/244 Fall 2016

Copyright © 2010-2014, E. A. Lee, J. Roychowdhury, S. A. Seshia, S. Tripakis, All rights reserved

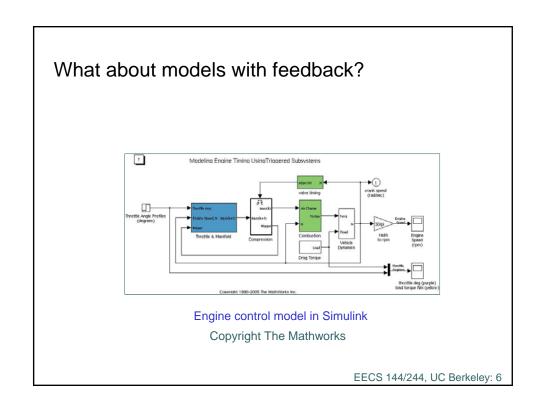

#### **Synchronous Composition**

Thanks to Edward A. Lee for several slides

### Composition of discrete systems

Two major paradigms:

### Synchronous:

All subsystems move together, in "lock-step".

<u>Application domains</u>: synchronous circuits, embedded control, ...

### **Asynchronous:**

Each subsystem moves at its own pace: interleaving. Application domains: concurrent software, distributed systems, ...

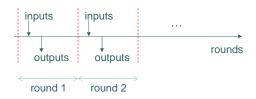

# Fundamental characteristic of synchronous systems

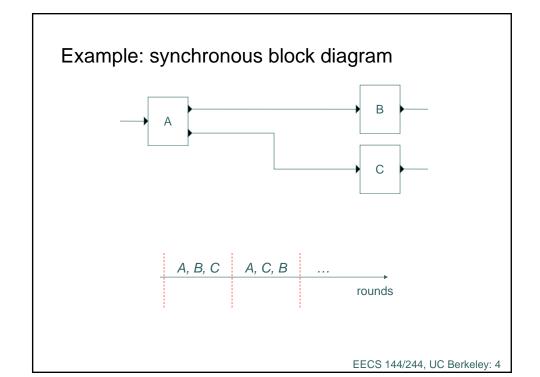

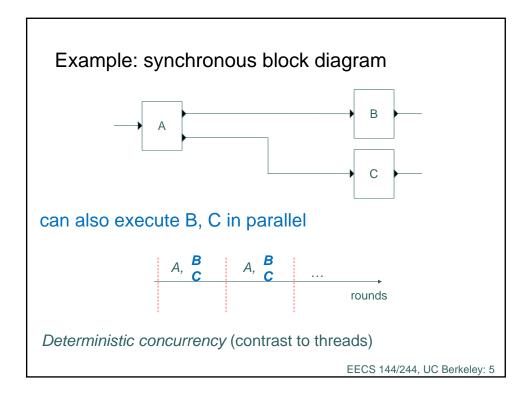

Notion of **synchronous round** (or **cycle**, or **reaction**)

All subsystems synchronize at beginning/end of round.

### Defining the semantics of synchronous feedback

Two basic approaches:

Non-deterministic semantics: used for verification (e.g., tools like NuSMV)

<u>Deterministic semantics</u>: used for implementation (e.g., circuits or synchronous languages)

EECS 144/244, UC Berkeley: 7

### Non-deterministic semantics

Main idea:

composition = **conjunction** of transition relations

### Composition as conjunction of transition relations

Systems A and B described symbolically:

Sets of variables (some may be common):  $X_A$ ,  $X_B$

Initial state formulas:  $init_A(X_A)$ ,  $init_B(X_B)$

Next state formulas:  $tr_A(X_A, X_A')$ ,  $tr_B(X_B, X_B')$

EECS 144/244, UC Berkeley: 9

### Composition as conjunction of transition relations

Composite system described by:

Set of variables:  $X_A \cup X_B$

Initial state formula:  $init_A(X_A) \wedge init_B(X_B)$

Next state formula:  $tr_A(X_A, X_A') \wedge tr_B(X_B, X_B')$

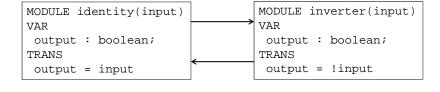

### Example: a model with feedback in NuSMV

EECS 144/244, UC Berkeley: 11

### Example: a model with feedback in NuSMV

Together:  $x = y \land y = \neg x$  No solution.

NuSMV issues warning about "fair states set" being empty.

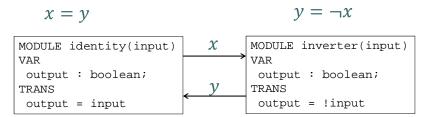

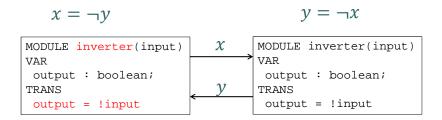

### Example: a model with feedback in NuSMV

Together:  $x = \neg y \land y = \neg x$

Two solutions.

NuSMV considers both states as reachable.

EECS 144/244, UC Berkeley: 13

# Modeling (for verification) vs. programming (implementing)

Non-deterministic semantics OK for verification: can be seen as over-approximation of all possible behaviors.

Synchronous models essential also for **programming**:

# Modeling (for verification) vs. programming (for implementation)

When programming, semantics need to be <u>well-defined</u> and <u>implementable</u>.

E.g., what circuit are we supposed to synthesize from this model?

$$x = \neg y \land y = \neg x$$

EECS 144/244, UC Berkeley: 15

# Modeling (for verification) vs. programming (for implementation)

When programming, semantics need to be <u>well-defined</u> and <u>implementable</u>.

E.g., what circuit are we supposed to synthesize from this model?

$$x = \neg y \land y = \neg x$$

ambiguous behavior

# Modeling (for verification) vs. programming (for implementation)

When programming, semantics need to be <u>well-defined</u> and implementable.

E.g., what circuit are we supposed to synthesize from this model?

$$x = \neg y \land y = \neg x$$

Guaranteed to stabilize?

EECS 144/244, UC Berkeley: 17

# Modeling (for verification) vs. programming (for implementation)

When programming, semantics need to be <u>well-defined</u> and <u>implementable</u>.

E.g., what circuit are we supposed to synthesize from this model?

$$x = \neg y \land y = \neg x$$

$0 \rightarrow 1 \rightarrow 0 \rightarrow \cdots$

Possible oscillation:

### Defining the semantics of synchronous feedback

Two basic approaches:

Non-deterministic semantics: used for verification

<u>Deterministic semantics</u>: used for implementation – two approaches to ensure determinism:

- Strict approach: Forbid instantaneous feedback: e.g., as in Lustre, SCADE, Simulink (unless if algebraic loops explicitly enabled)

- 2. **Non-strict approach**: Constructive fixpoint semantics: e.g., as in Esterel, Ptolemy

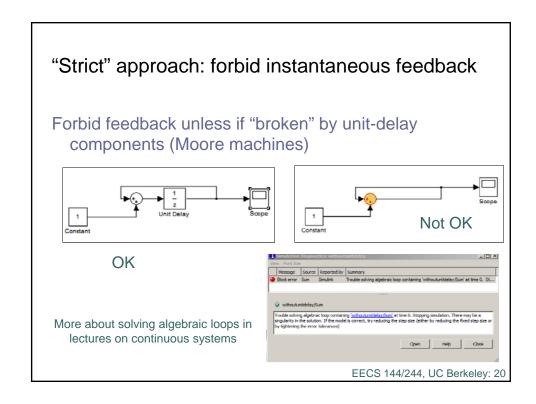

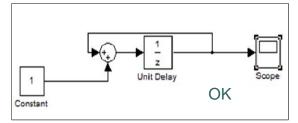

### "Strict" approach: forbid instantaneous feedback

Forbid feedback unless if "broken" by unit-delay components (Moore machines)

Why does this work?

At the beginning of each cycle, outputs of Moore machines are known => acyclic dependency graph.

EECS 144/244, UC Berkeley: 21

### Defining the semantics of synchronous feedback

Two basic approaches:

Non-deterministic semantics: used for verification (e.g., tools like NuSMV)

<u>Deterministic semantics</u>: used for programming – two approaches to ensure determinism:

- 1. **Strict approach**: Forbid instantaneous feedback

- 2. Non-strict approach: Constructive fixpoint semantics

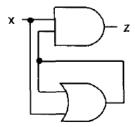

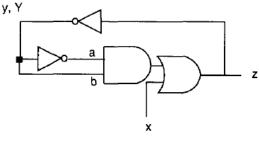

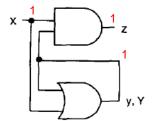

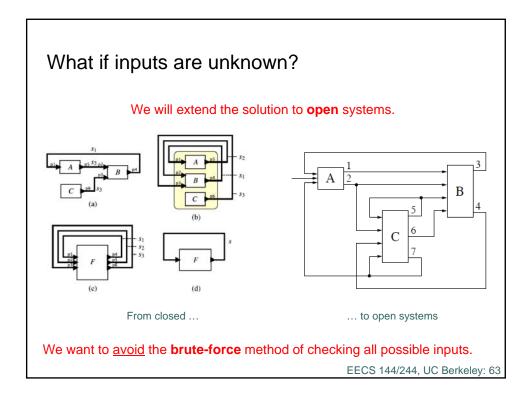

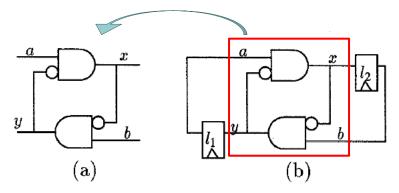

### Strict approach is sometimes too strict

Some circuits have cycles, but their output is well-defined for all inputs.

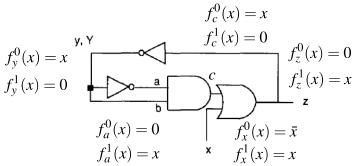

Fig. 1. Cyclic Combination Circuits: A Simple Example.

[Malik, Trans. on CAD, 1994]

EECS 144/244, UC Berkeley: 23

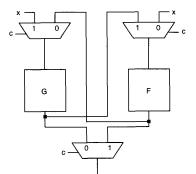

### Practical cyclic combinational circuits

z = if(c)then F(G(x)) else G(F(x))

Is there an equivalent acyclic circuit?

[Malik, Trans. on CAD, 1994]

### Esterel:

### A Synchronous/Reactive Programming Language

present I then

present S then emit T end

else

present T then emit S end

end

"There is a path from S to T and a path from T to S, hence a cycle. However, it is obvious from the source code that only one path can be used at a time, and, therefore, that the circuit is well-behaved."

[Shiple, Berry, and Touati, 1996]

EECS 144/244, UC Berkeley: 25

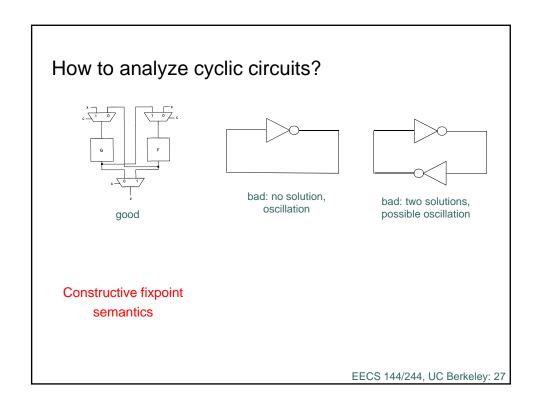

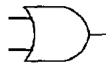

### "Good" and "bad" cyclic circuits

bad: no solution, oscillation

bad: two solutions, possible oscillation

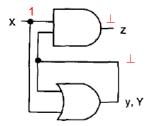

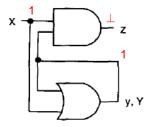

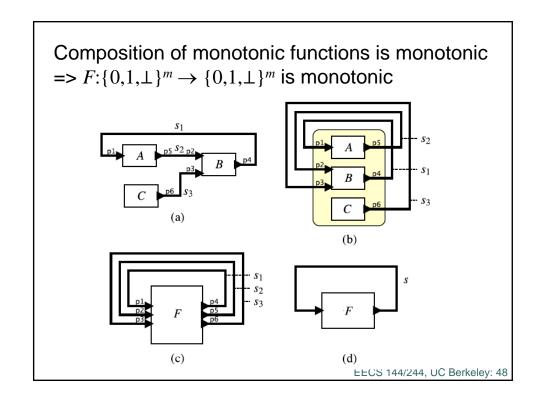

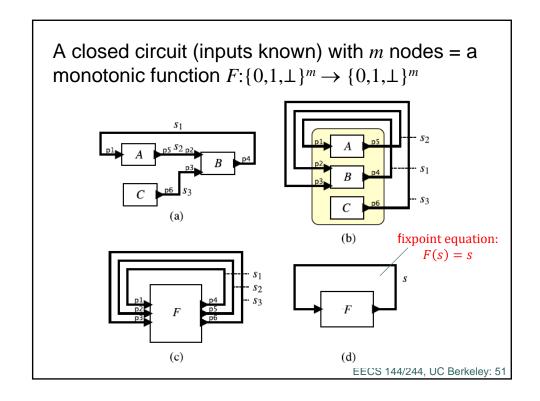

# Analyzing cyclic circuits using the constructive fixpoint approach: basic idea

Start with all signal values unknown (denoted ⊥: "bottom")

Try to derive known values based on circuit logic.

Iterate until no more known values can be derived.

If all values known, circuit is good.

Analyzing cyclic circuits using the constructive fixpoint approach: example

EECS 144/244, UC Berkeley: 29

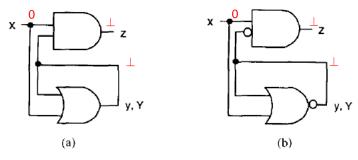

Analyzing cyclic circuits using the constructive fixpoint approach: example

Fixpoint reached.

# Analyzing cyclic circuits using the constructive fixpoint approach: other examples

EECS 144/244, UC Berkeley: 31

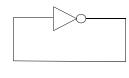

# Constructive semantics (ternary logic) vs. classic logic

We could interpret our circuits also in classic logic: only 0, 1 (true, false). No "unknown" ( $\perp$ ) value.

But there are bad circuits with unique fixpoints in classic logic:

Logically, the output of the AND gate is 0. But if x=0, and the inverters have delay, then this circuit will oscillate.

### Applying the procedure

Initialize with input values and "unknown" on other nodes.

[Malik, Trans. on CAD, 1994]

EECS 144/244, UC Berkeley: 33

### Applying the procedure

Evaluate lower gate.

[Malik, Trans. on CAD, 1994]

### Applying the procedure

Evaluate gates in arbitrary order until nothing changes.

Does this mean the circuit is valid ("constructive")?

Not necessarily: must try all other possible inputs

At this point, all nodes are known => fixpoint reached.

EECS 144/244, UC Berkeley: 35

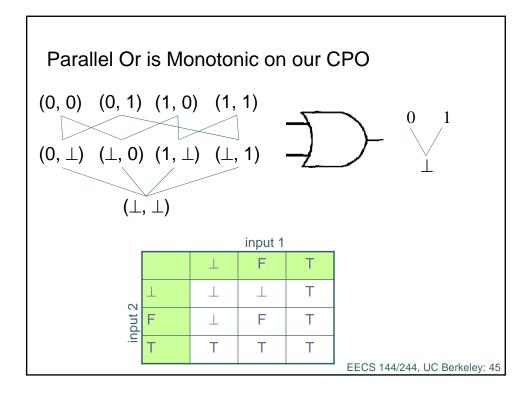

# Implicitly using Parallel (Non-Strict) Or

The non-strict or (often called the "parallel or") can produce a known output even if the input is not completely know. Here is a table showing the output as a function of two inputs:

Extending gates in "ternary" (constructive) logic

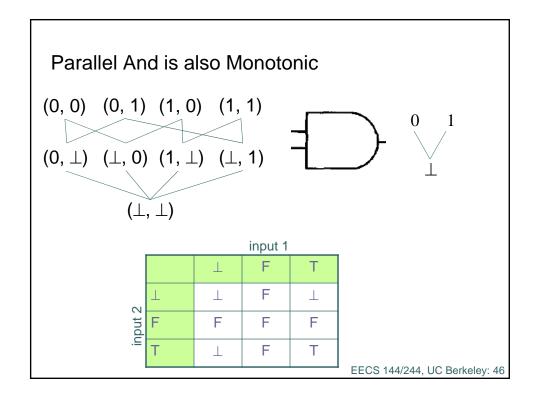

# Implicitly using Parallel (Non-Strict) And

The non-strict and (often called the "parallel and") can produce a known output even if the input is not completely know. Here is a table showing the output as a function of two inputs:

|         |   | input 1 |   |   |  |

|---------|---|---------|---|---|--|

| input 2 |   | Т       | F | Т |  |

|         |   | Т       | F | Т |  |

|         | F | F       | F | F |  |

|         | Т | Т       | F | Т |  |

EECS 144/244, UC Berkeley: 37

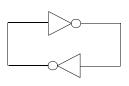

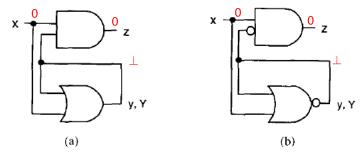

### Applying the procedure with input 0 on our circuit and a variant of it

Initialize with input values and "unknown" on other nodes.

Fig. 4. Cyclic combinational circuits with sequential parts.

[Malik, Trans. on CAD, 1994]

### Applying the procedure with input 0 on our circuit and a variant of it

Evaluate gates in arbitrary order until no progress is made.

Fig. 4. Cyclic combinational circuits with sequential parts.

Unknown nodes remain. Constructive semantics rejects these circuits.

EECS 144/244, UC Berkeley: 39

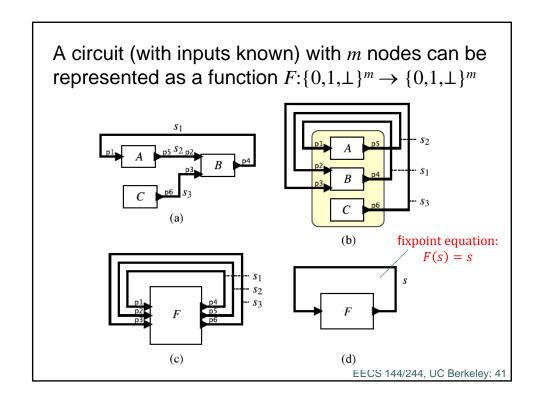

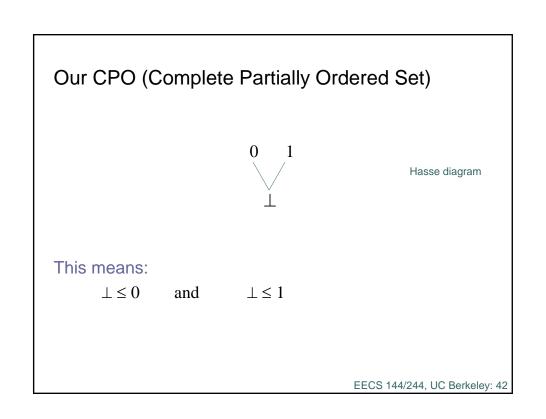

### **Key Property**

The procedure always converges to a unique solution for all nodes.

The solution may contain unknown values!  $(\bot)$

That solution is the least fixed point of a monotonic function on a complete partial order (CPO).

The Kleene fixed-point theorem assures that such a least fixed point exists, is unique, and can be found via this procedure.

### Product CPO on Pairs

$$(0,0)$$

$(0,1)$   $(1,0)$   $(1,1)$   $(0,\bot)$   $(\bot,0)$   $(1,\bot)$   $(\bot,1)$  Hasse diagram  $(\bot,\bot)$

This means:

$$(\bot,0) \le (1,0)$$

$(\bot,1) \le (1,1)$  ...

This generalizes to arbitrary *m*-tuples.

Height is m+1

EECS 144/244, UC Berkeley: 43

### Monotonic (Order Preserving) Functions

Let  $(A, \leq)$  and  $(B, \leq)$  be posets.

A function  $f: A \rightarrow B$  is called *monotonic* if

$$a \le a' \implies f(a) \le f(a')$$

### What about logical NOT?

What does the extended truth table (with "uknown") for NOT look like?

Is NOT monotonic?

# Fundamental Algorithms for System Modeling, Analysis, and Optimization

### Stavros Tripakis

UC Berkeley EECS 144/244 Fall 2016

Copyright © 2010-2013, E. A. Lee, J. Roychowdhury, S. A. Seshia, S. Tripakis, All rights reserved

Synchronous Composition – Part 2

Thanks to Edward A. Lee for several slides

### Defining the semantics of synchronous feedback

Two basic approaches:

Non-deterministic semantics: used for verification (e.g., tools like NuSMV)

<u>Deterministic semantics</u>: used for programming – two approaches to ensure determinism:

- 1. **Strict approach**: Forbid instantaneous feedback

- 2. Non-strict approach: Constructive fixpoint semantics

Partial orders: basics

EECS 144/244, UC Berkeley: 52

### **Partial Orders**

A *partial order* on the set A is a binary relation  $\leq$  that is, for all  $a, b, c \in A$ ,

o reflexive:  $a \le a$

• antisymmetric:  $a \le b$  and  $b \le a \Rightarrow a = b$

• transitive:  $a \le b$  and  $b \le c \Rightarrow a \le c$

A partially ordered set (poset) is a set A and a binary relation  $\leq$ , written  $(A, \leq)$ .

EECS 144/244, UC Berkeley: 53

#### **Total Orders**

Elements a and b of a poset  $(A, \leq)$  are *comparable* if either  $a \leq b$  or  $b \leq a$ . Otherwise they are *incomparable*.

A poset  $(A, \leq)$  is *totally ordered* if every pair of elements is comparable.

Totally ordered sets are also called *linearly ordered sets* and *chains*.

### Examples

- 1. 0 < 1

- 2. 1 < ∞

- 3. child < parent

- 4. child > parent

- 5. 11,000/3,501 is a better approximation to  $\pi$  than 22/7

- 6. integer n is a divisor of integer m.

- 7. Set A is a subset of set B.

Which of these are partial orders? Total orders? Which are the corresponding posets?

EECS 144/244, UC Berkeley: 55

### **Fixed Point Theorem**

(a variant of the Kleene fixed-point theorem)

Let  $(A, \leq)$  be the CPO  $\{0,1,\perp\}^m$  (on m-tuples) Let  $f: A \to A$  be a monotonic function Let  $C = \{f^n(\perp), n \in \{1, ..., m\}\}$

$\vee C = f^m(\bot)$  is the *least* fixed point of f

Intuition: The least fixed point of a monotonic function is obtained by applying the function first to unknown, then to the result, then to that result, etc.

Bounded by the height of the CPO, m.

### Join (Least Upper Bound)

An *upper bound* of a subset  $B \subseteq A$  of a poset  $(A, \leq)$  is an element  $a \in A$  such that for all  $b \in B$  we have  $b \leq a$ .

A *least upper bound* (LUB) or *join* of B is an upper bound a such that for all other upper bounds a' we have  $a \le a'$ .

The *join* of *B* is written  $\vee$  *B*.

When the join of *B* exists, then *B* is said to be *joinable*.

EECS 144/244, UC Berkeley: 57

### Least Upper Bound – Examples

$$(0,0)$$

$(0,1)$   $(1,0)$   $(1,1)$   $(0,\bot)$   $(\bot,0)$   $(1,\bot)$   $(\bot,1)$  Hasse diagram  $(\bot,\bot)$

Does the upper bound exist for

$$\{(0,\perp), (\perp, 0)\}$$

?

$$\{(0,\perp), (\perp, 1)\}$$

?

Does the upper bound exist for: 0<1<2<...?

### Proof of Theorem (part 1: $\vee$ *C* is a fixed point)

Note that *C* is a chain in a finite poset:

$$\bot \le f(\bot)$$

$f(\bot) \le f^2(\bot)$  by monotonicity

...

$f^{m-1}(\bot) \le f^m(\bot)$

Since the longest chain in the poset has length m+1, this sequence has to stop increasing and settle to a fixed point:  $f^{k-1}(\bot) = f^k(\bot)$  for some k.

Moreover,  $f^k(\bot) = \lor C$ . Hence,  $\lor C$  is a fixed point of f.

EECS 144/244, UC Berkeley: 59

# Proof of Theorem (part 2: $\vee$ *C* is the least fixed point)

Let a be another fixed point: f(a) = aShow that  $\vee C$  is the least fixed point:  $\vee C \leq a$ Since f is monotonic:

$$\bot \le a$$

$f(\bot) \le f(a) = a$  ...  $f^m(\bot) \le f^m(a) = a$  So  $a$  is an upper bound of the chain  $C$ , hence  $\lor C \le a$ .

### Brute Force Application of the Theorem

- Start with signals "unknown" at all nodes of the circuit.

- Evaluate components (gates) in arbitrary order repeatedly until no further progress is made.

- If the result has all signals "known," then declare it to be the constructive solution.

- Otherwise, reject model as nonconstructive (buggy).

EECS 144/244, UC Berkeley: 61

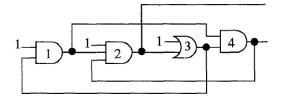

### Does evaluation order matter?

In the circuit below, evaluation order matters:

- 1, 2, 3, 4: requires three passes to converge.

- 3, 1, 4, 2: requires one pass to converge.

There exists research to optimize this [see paper by Edwards-Lee]

Figure 3: Number of gate evaluations depends on evaluation order.

[Shiple, Berry, and Touati, 1996]

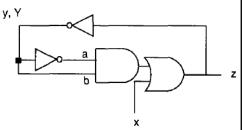

### Instead: use symbolic execution

Main idea: instead of iterating over **values**, iterate over **functions**:

- Start with unknown *function of the inputs* at all nodes except inputs.

- Update the functions in arbitrary order repeatedly until no further progress is made.

- If the result has all functions known, then declare the circuit constructive.

### Symbolic execution

Assume a single binary input (for now). For each node a in the circuit, define a function from the input to the node value:

$$f_a \colon \{0,1\} \to \{\bot,0,1\}$$

These give the outputs as a function of x only.

EECS 144/244, UC Berkeley: 65

### Symbolic execution strategy

Start with all nodes except inputs being given by the unknown function:

$$f_y(x) = \bot$$

$f_a(x) = \bot$

$f_b(x) = \bot$

$f_z(x) = \bot$

$f_z(x) = \bot$

Then update these functions iteratively until convergence. But how to update the functions?

First: how to represent the functions

Represent each function of the form:

$$f_a \colon \{0,1\} \to \{\bot,0,1\}$$

using two characteristic functions of the form:

$$f_a^0: \{0,1\} \rightarrow \{0,1\}$$

$f_a^1: \{0,1\} \rightarrow \{0,1\}$

where

$$f_a^0(x) = \left\{ egin{array}{ll} 1 & \mbox{if } f_a(x) = 0 \\ 0 & \mbox{otherwise} \end{array}

ight. \qquad f_a^1(x) = \left\{ egin{array}{ll} 1 & \mbox{if } f_a(x) = 1 \\ 0 & \mbox{otherwise} \end{array}

ight.$$

How can these be represented in practice?

Using **BDDs**!

EECS 144/244, UC Berkeley: 67

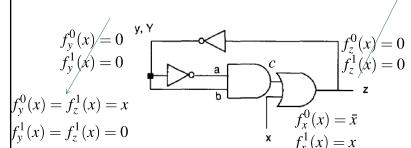

# Symbolic execution strategy using characteristic functions

Start with all nodes except inputs being given by the unknown function:

$$f_{y}^{0}(x) = 0 \\ f_{y}^{0}(x) = 0 \\ f_{z}^{0}(x) = 0 \\ f_{z}^{0}(x) = 0 \\ f_{z}^{0}(x) = 0 \\ f_{z}^{0}(x) = 0 \\ f_{z}^{1}(x) = 0 \\ f_{z}^{1}(x$$

Then update these functions iteratively until convergence. But how to update the functions?

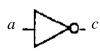

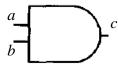

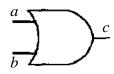

### Operating on characteristic functions

Gates relate characteristic functions of the outputs with those of the inputs:

$$f_c^0(x) = f_a^1(x)$$

$f_c^1(x) = f_a^0(x)$

$$f_c^0(x) = f_a^0(x) + f_b^0(x)$$

$$\begin{split} f_c^0(x) &= f_a^1(x) & f_c^0(x) = f_a^0(x) + f_b^0(x) & f_c^0(x) = f_a^0(x) \cdot f_b^0(x) \\ f_c^1(x) &= f_a^0(x) & f_c^1(x) = f_a^1(x) \cdot f_b^1(x) & f_c^1(x) = f_a^1(x) + f_b^1(x) \end{split}$$

EECS 144/244, UC Berkeley: 69

Symbolic execution strategy using

characteristic functions

$f_z^0(x) = f_c^0(x) \cdot f_x^0(x) = 0 \cdot \bar{x} = 0$  $f_z^1(x) = f_c^1(x) + f_x^1(x) = 0 + x = x$

Update nodes in arbitrary order:

etc.

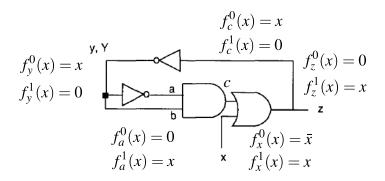

### Convergence

Quickly converge to these characteristic functions:

How do we know whether the circuit is constructive?

EECS 144/244, UC Berkeley: 71

### Checking whether circuit is constructive

Quickly converge to these characteristic functions:

Circuit is constructive iff at all nodes a we have for all x

$$f_a^0(x) + f_a^1(x) = 1$$

i.e. the value is known! (Checking this is a SAT problem)

### Does the procedure always converge? Is the answer unique?

Consider a poset  $\{0, 1\}$  where 0 < 1.

This induces a poset on the set of functions of form:

$$f_a^i: \{0,1\} \to \{0,1\}$$

How?

This poset has a bottom element: the function

$$f_{\perp}^{i}(x) = 0$$

This poset is finite, with structure much like the flat order. The Kleene fixed-point theorem applies. Extends easily to tuples of functions.

EECS 144/244, UC Berkeley: 73

### Gate operations on characteristic functions are monotonic functions!

These are monotonic in the sense that if you know more about the inputs, then you learn more about the outputs:

$$\begin{split} (f_a^0,f_a^1) &\leq (g_a^0,g_a^1) \Rightarrow (f_c^0,f_c^1) \leq (g_c^0,g_c^1) \\ ((f_a^0,f_b^0),(f_a^1,f_b^1)) &\leq ((g_a^0,g_b^0),(g_a^1,g_b^1)) \Rightarrow (f_c^0,f_c^1) \leq (g_c^0,g_c^1) \end{split}$$

$$f_c^0(x) = f_a^0(x)$$

$f_a^1(x) = f_a^0(x)$

$$f_c^0(x) = f_a^1(x)$$

$f_c^0(x) = f_a^0(x) + f_b^0(x)$   $f_c^0(x) = f_a^0(x) \cdot f_b^0(x)$

$$f_c^1(x) = f_a^1(x) \cdot f_b^1(x)$$

$$f_c^0(x) = f_a^1(x) \qquad f_c^0(x) = f_a^0(x) + f_b^0(x) \qquad f_c^0(x) = f_a^0(x) \cdot f_b^0(x)$$

$$f_c^1(x) = f_a^0(x) \qquad f_c^1(x) = f_a^1(x) \cdot f_b^1(x) \qquad f_c^1(x) = f_a^1(x) + f_b^1(x)$$

### Extension to sequential circuits: circuits with state

Figure 1: Circuits are well-behaved unless a = b = 1.

First need to find which inputs are problematic, if any.

Then need to determine whether those inputs can occur (reachability analysis on a state machine)

[Shiple, Berry, and Touati, DATE, 1996]

EECS 144/244, UC Berkeley: 75

### **Asynchronous Composition**

See 11-asynchronous.pdf

### Bibliography

Malik, S. (1994). Analysis of cyclic combinational circuits. IEEE Trans. Computer-Aided Design, 13(7):950–956.

Edwards, S. and Lee, E. (July 2003). The semantics and execution of a synchronous block-diagram language. Science of Computer Programming, 48:21–42(22).

Shiple, T., Berry, G., and Touati, H. (1996). Constructive analysis of cyclic circuits. In European Design and Test Conference (EDTC'96). IEEE Computer Society.

Berry, G. (1999). The Constructive Semantics of Pure Esterel.

Davey, B. A. and Priestley, H. A. (2002). Introduction to Lattices and Order. Cambridge University Press, 2nd edition.