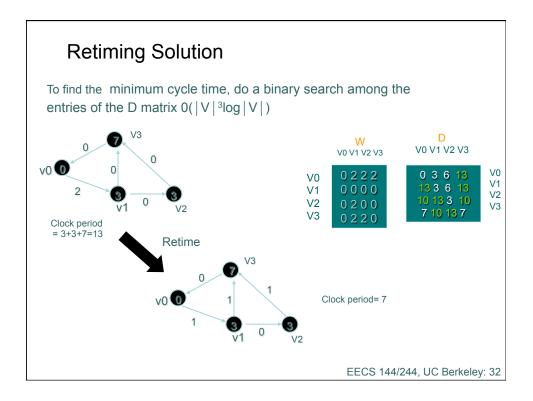

## Drawbacks of this Algorithm

- Requires W/D matrix computation

- O(|V|<sup>2</sup>) clock period constraints, most of which are redundant

- Average case is worst case

Fortunately, there's another algorithm we can use:

- "relaxation-based" algorithm called FEAS

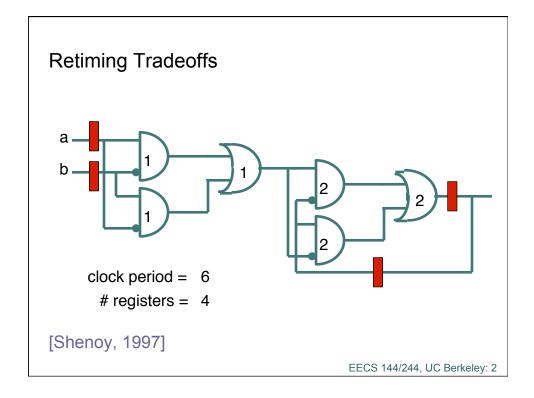

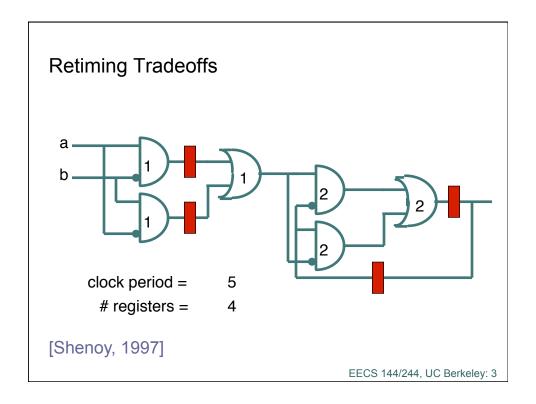

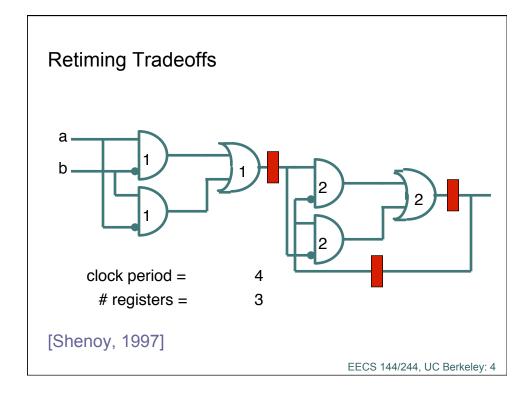

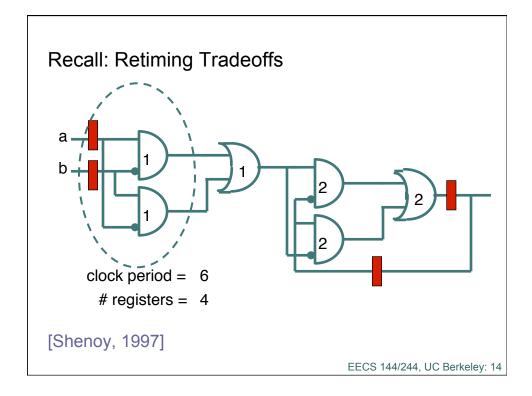

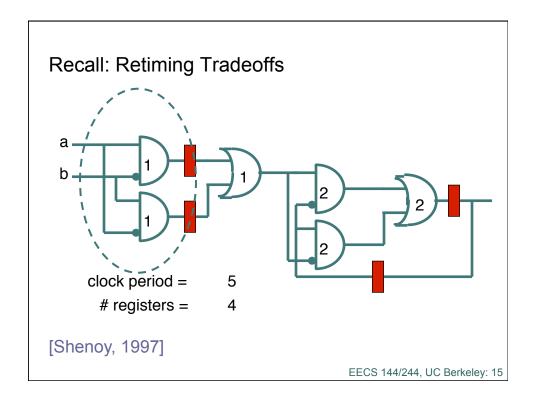

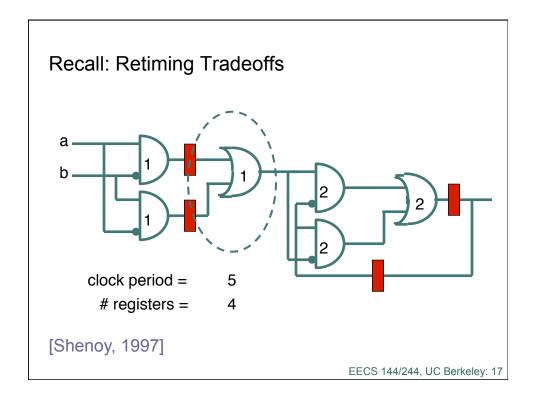

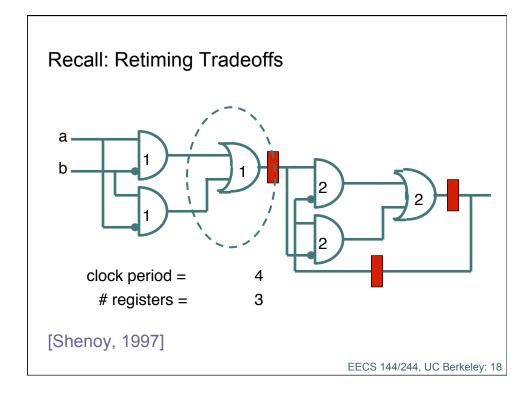

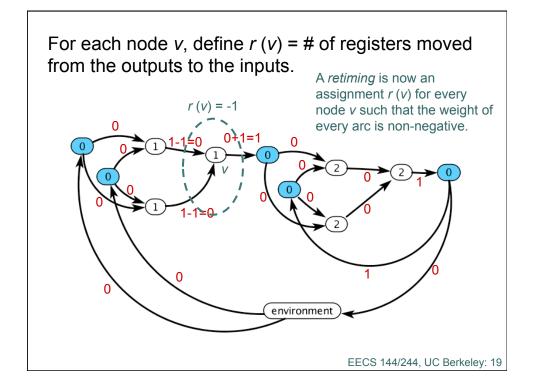

- See: [Shenoy, 1997]

EECS 144/244, UC Berkeley: 33

## References

- 1. Leiserson, C. E. and J. B. Saxe (1983). "Optimizing synchronous systems." *Journal of VLSI and Computer Systems*: pp. 41-67.

- 2. Leiserson, C. E. and J. B. Saxe (1991). "Retiming synchronous circuitry." *Algorithmica* 6(1): pp. 5-35.

- 3. Shenoy, N. (1997). "Retiming: Theory and practice." *Integration, the VLSI Journal* 22: pp. 1-21.

EECS 144/244, UC Berkeley: 41