### SPARK: A Parallelizing High-Level Synthesis Framework

#### Sumit Gupta

### Rajesh Gupta, Nikil Dutt, Alex Nicolau

Center for Embedded Computer Systems University of California, Irvine and San Diego http://www.cecs.uci.edu/~spark

Supported by Semiconductor Research Corporation & Intel Inc

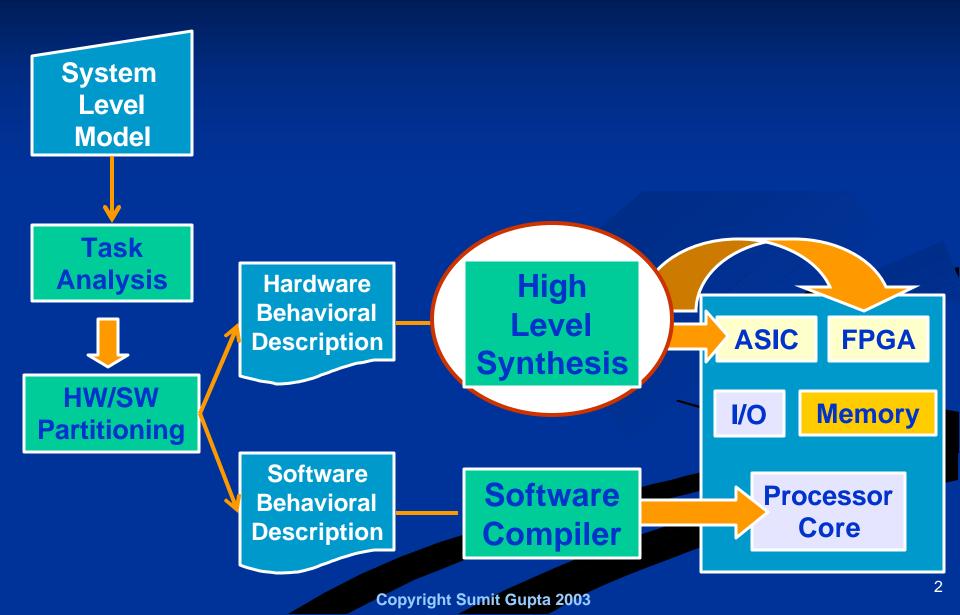

## **System Level Synthesis**

## **High Level Synthesis**

Transform behavioral descriptions to RTL/gate level

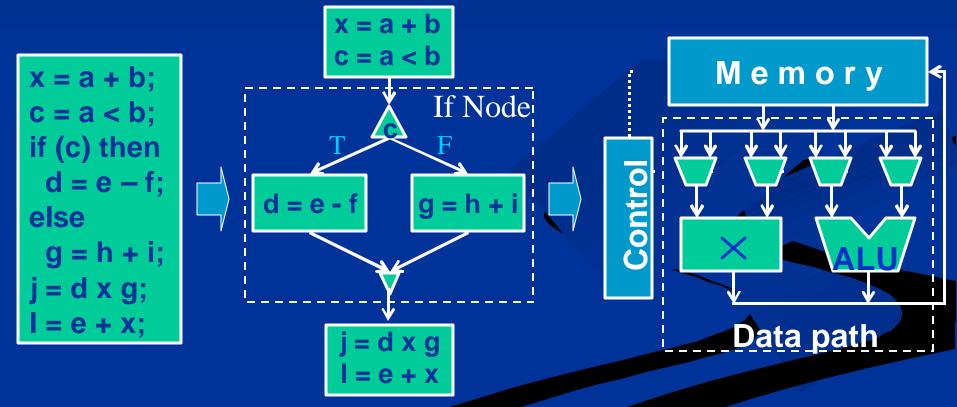

From C to CDFG to Architecture

## **High Level Synthesis**

Transform behavioral descriptions to RTL/gate level

From C to CDFG to Architecture

## Outline

Motivation and Background Our Approach to *Parallelizing* High-Level Synthesis Code Transformations Techniques for PHLS Parallelizing Transformations Dynamic Transformations The PHLS Framework and Experimental Results Multimedia and Image Processing Applications Case Study: Intel Instruction Length Decoder-Conclusions and Future Work

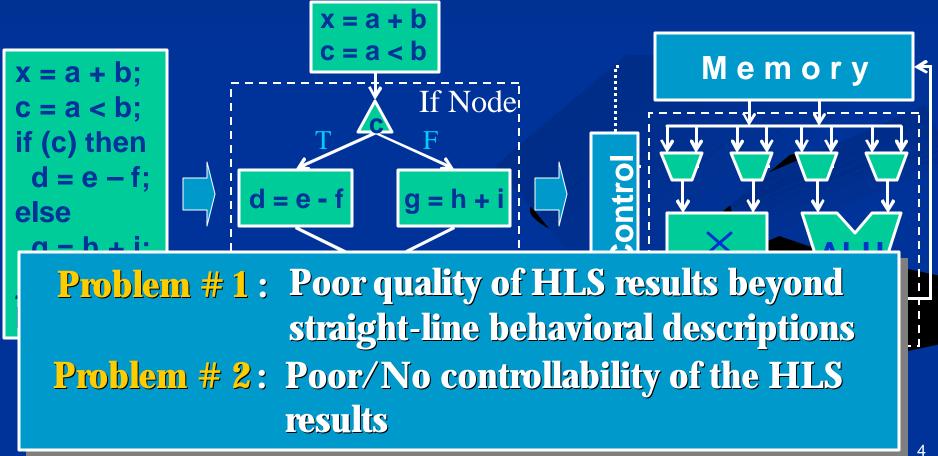

## **High-level Synthesis**

Well-researched area: from early 1980's

- Renewed interest due to new system level design methodologies

- Large number of synthesis optimizations have been proposed

- Either operation level: algebraic transformations on DSP codes

- or logic level: Don't Care based control optimizations

- In contrast, compiler transformations operate at both operation level (fine-grain) and source level (coarse-grain)

- Parallelizing Compiler Transformations

- Different optimization objectives and cost models than HLS

Our aim: Develop Synthesis and Parallelizing Compiler Transformations that are "useful" for HLS

- Beyond scheduling results: in Circuit Area and Delay

- For large designs with complex control flow (nested conditionals/loops)

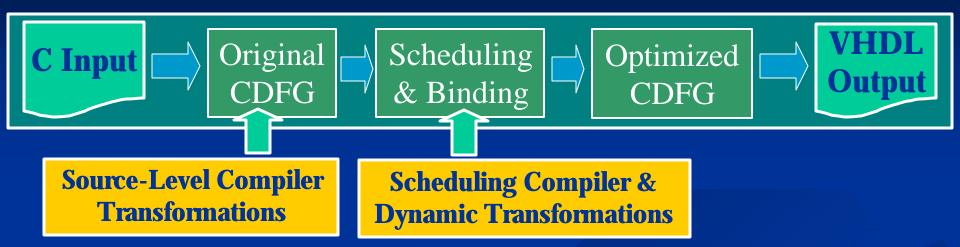

## **Our Approach: Parallelizing HLS (PHLS)**

Optimizing Compiler and Parallelizing Compiler transformations applied at Source-level (Pre-synthesis) and during Scheduling

- Source-level code refinement using Pre-synthesis transformations

- Code Restructuring by Speculative Code Motions

- Operation replication to improve concurrency

- Dynamic transformations: exploit new opportunities during scheduling

PHLS Transformations

Organized into Four Groups

1. Pre-synthesis: Loop-invariant code motions, Loop unrolling, CSE

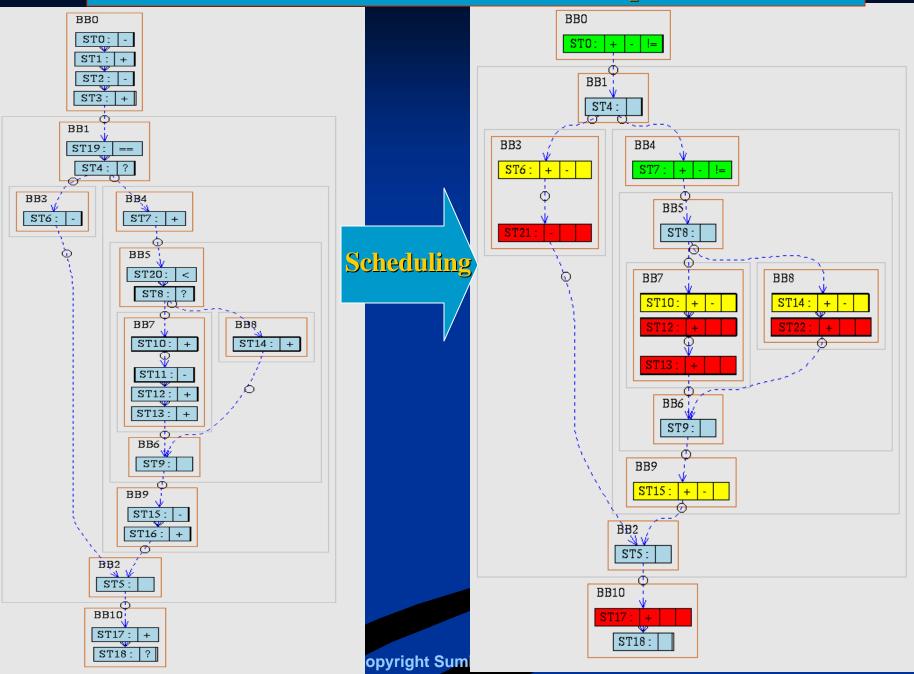

**2.** Scheduling: Speculative Code Motions, Multicycling, Operation Chaining, Loop Pipelining

**3**. **Dynamic**: Transformations applied dynamically during scheduling: Dynamic CSE, Dynamic Copy Propagation, Dynamic Branch Balancing

4. Basic Compiler Transformations: Copy Propagation, Dead Code Elimination

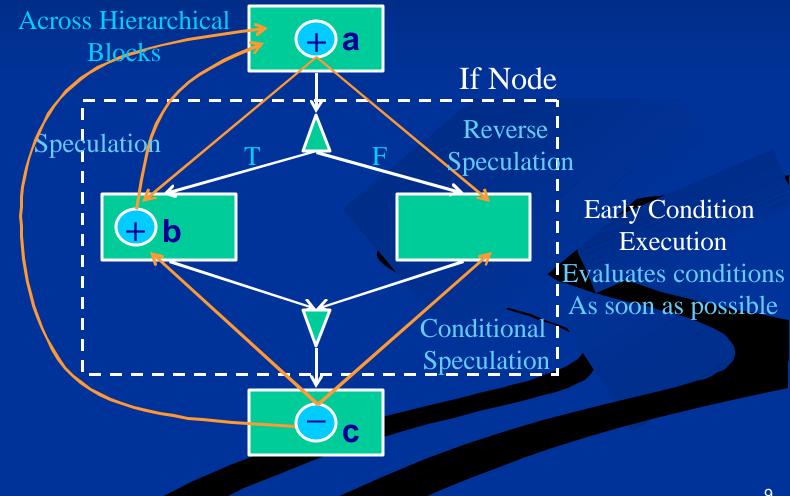

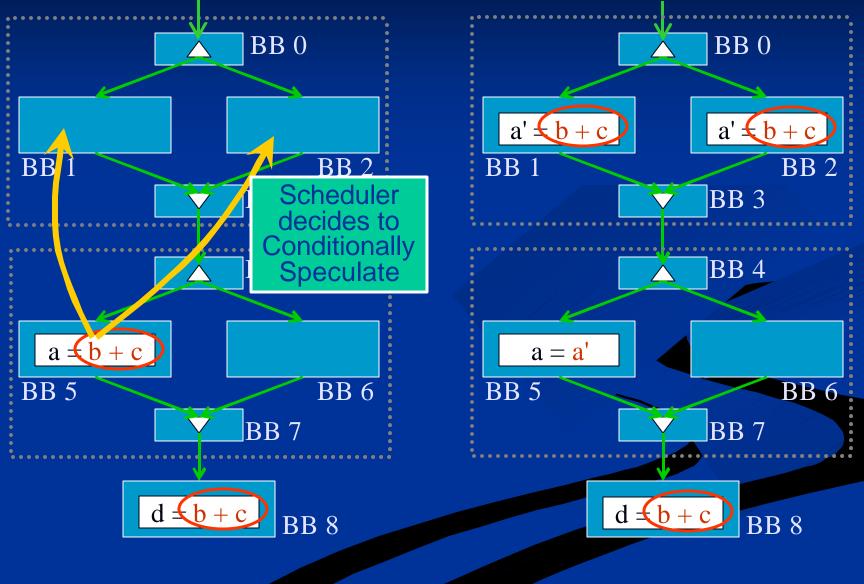

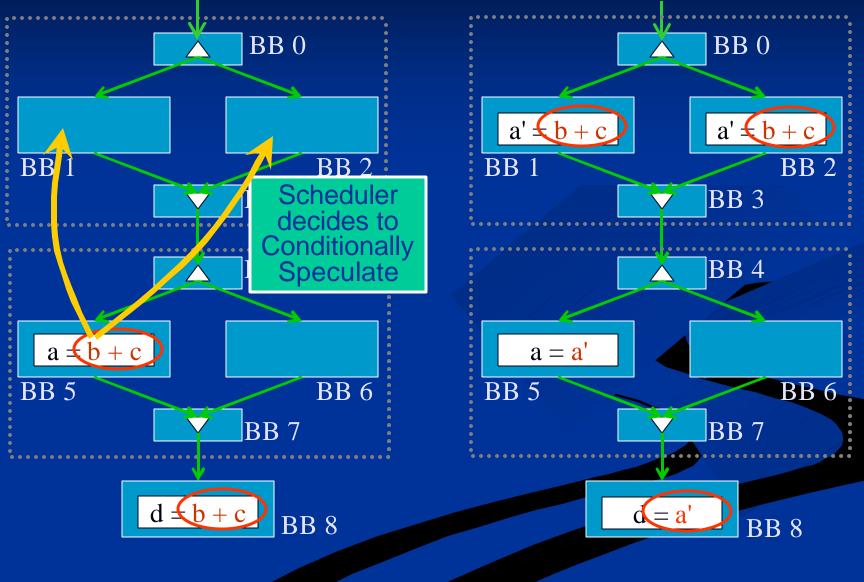

## **Speculative Code Motions**

**Operation Movement to reduce impact of Programming Style on Quality of HLS Results**

## **Dynamic Transformations**

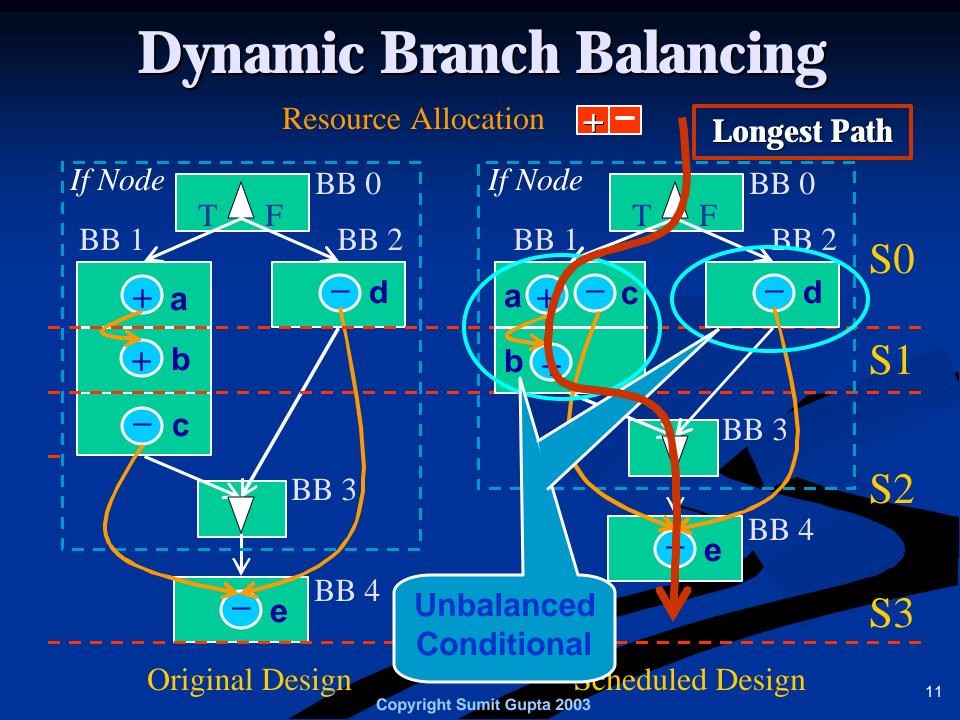

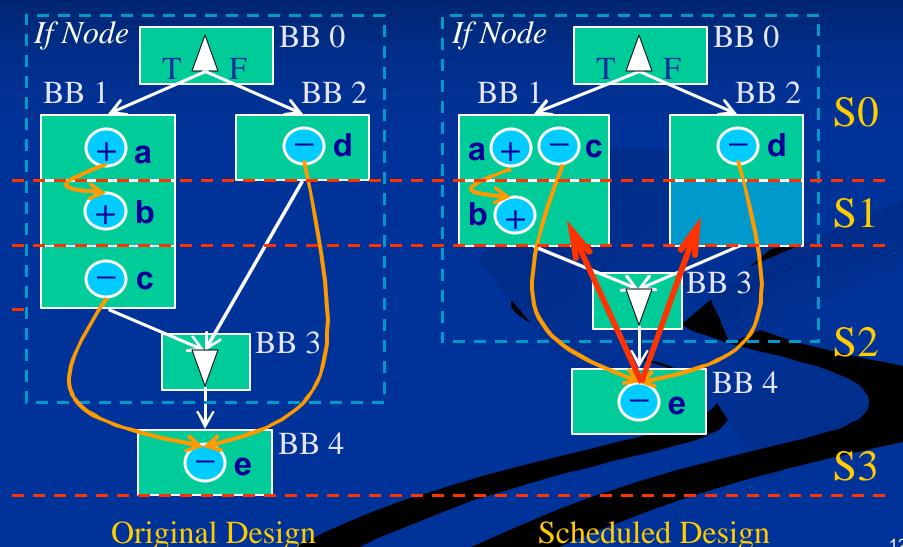

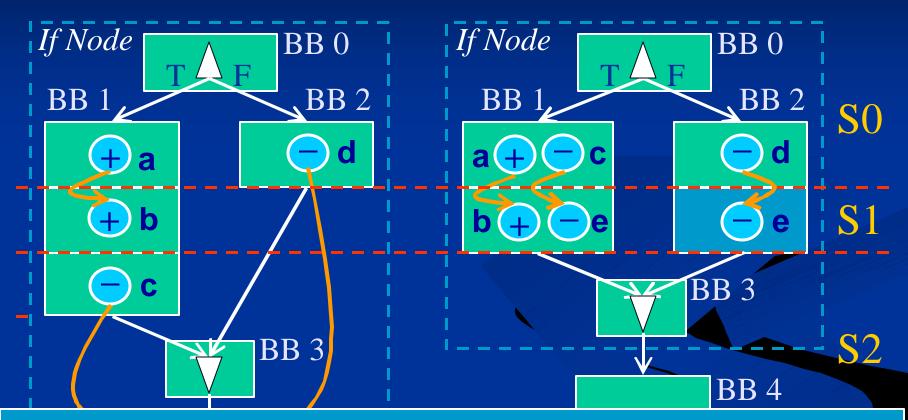

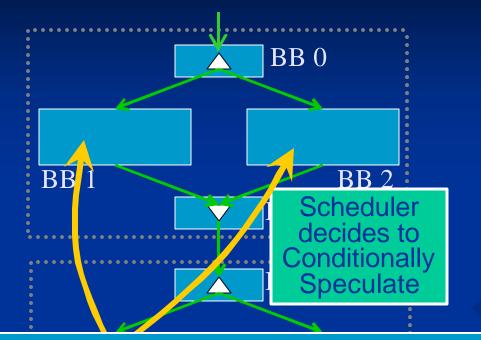

Called "dynamic" since they are applied during scheduling (versus a pass before/after scheduling) Dynamic Branch Balancing Increase the scope of code motions Reduce impact of programming style on HLS results Dynamic CSE and Dynamic Copy Propagation Exploit the Operation movement and duplication due to speculative code motions Create new opportunities to apply these transformations Reduce the number of operations

### **Insert New Scheduling Step in Shorter Branch**

Resource Allocation

Copyright Sumit Gupta 2003

### **Insert New Scheduling Step in Shorter Branch**

Resource Allocation

Dynamic Branch Balancing inserts new scheduling steps

Enables Conditional Speculation

Leads to further <u>code compaction</u>

Copyright Sumit Gupta 2003

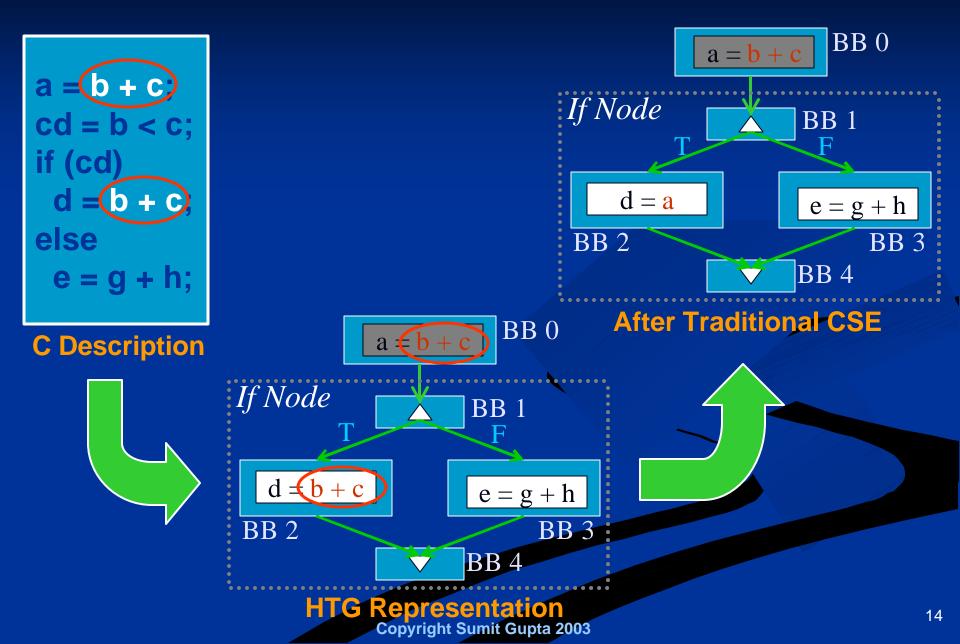

### **Dynamic CSE:** Going beyond Traditional CSE

### **Dynamic CSE:** Going beyond Traditional CSE

We use notion of Dominance of Basic Blocks

Basic block BBi dominates BBj if all control paths from the initial basic block of the design graph leading to BBj goes through BBi

We can eliminate an operation opj in BBj using common expression in opi if BBi dominates BBj

Copyright Sumit Gupta 2003

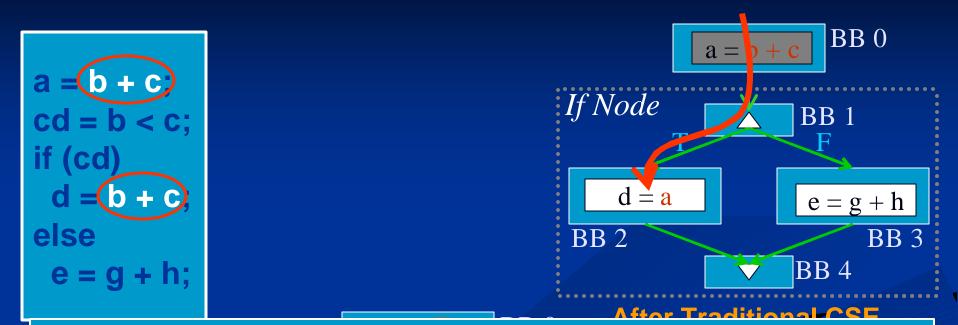

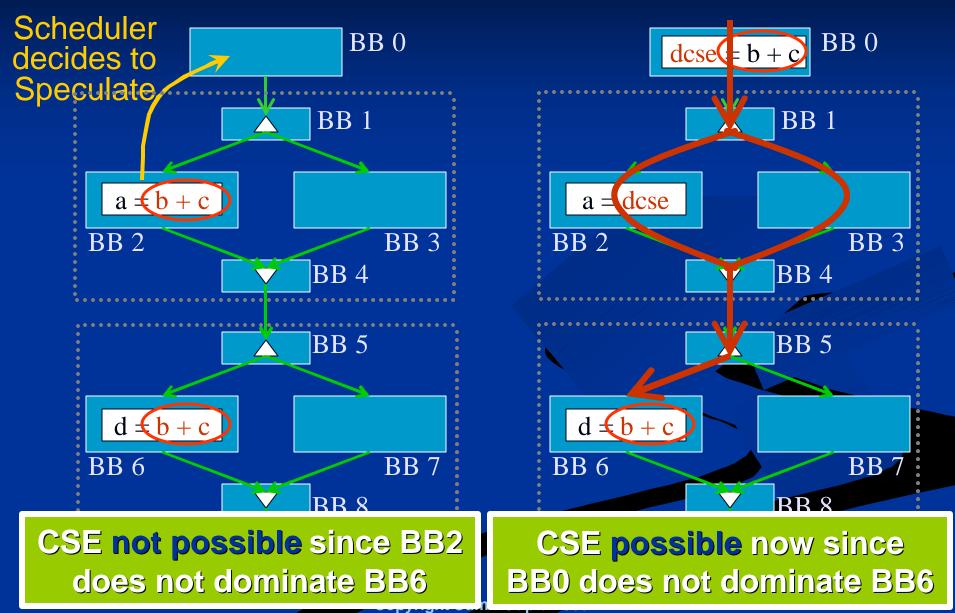

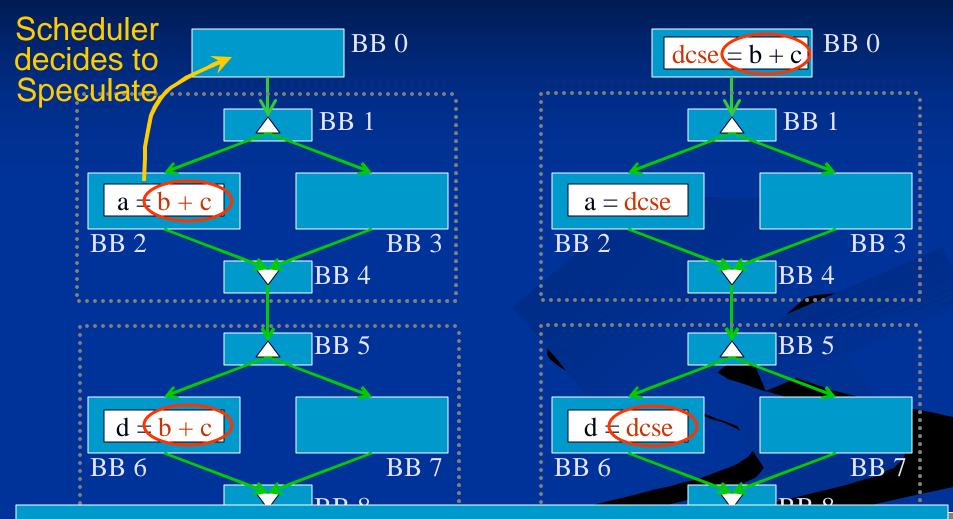

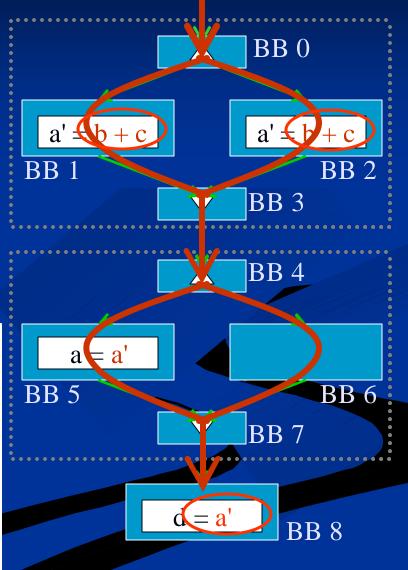

### New Opportunities for "Dynamic" CSE Due to Code Motions

### New Opportunities for "Dynamic" CSE Due to Code Motions

If scheduler moves or duplicates an operation op, apply CSE on remaining operations using op

### **Condition Speculation & Dynamic CSE**

### **Condition Speculation & Dynamic CSE**

### **Condition Speculation & Dynamic CSE**

Use the notion of dominance by groups of basic blocks

All Control Paths leading up to BB8 come from either BB1 or BB2: => BB1 and BB2 together dominate BB8

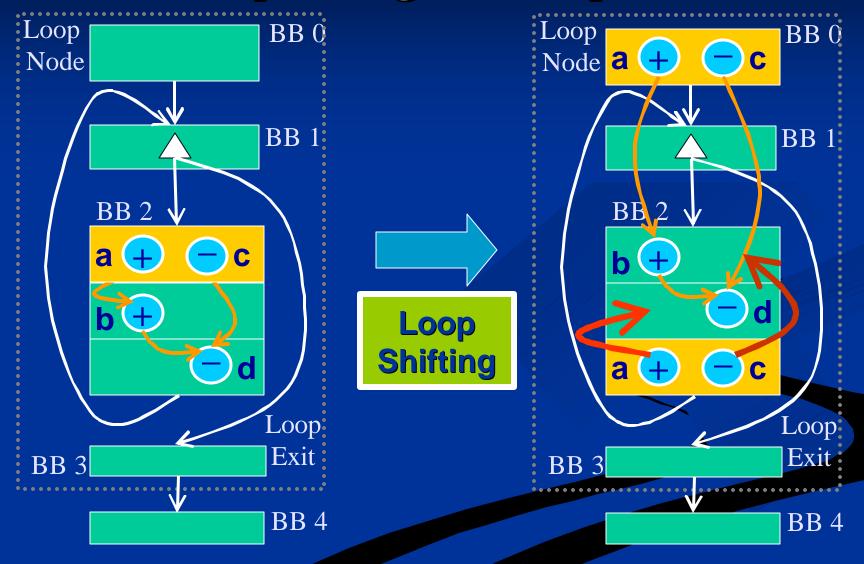

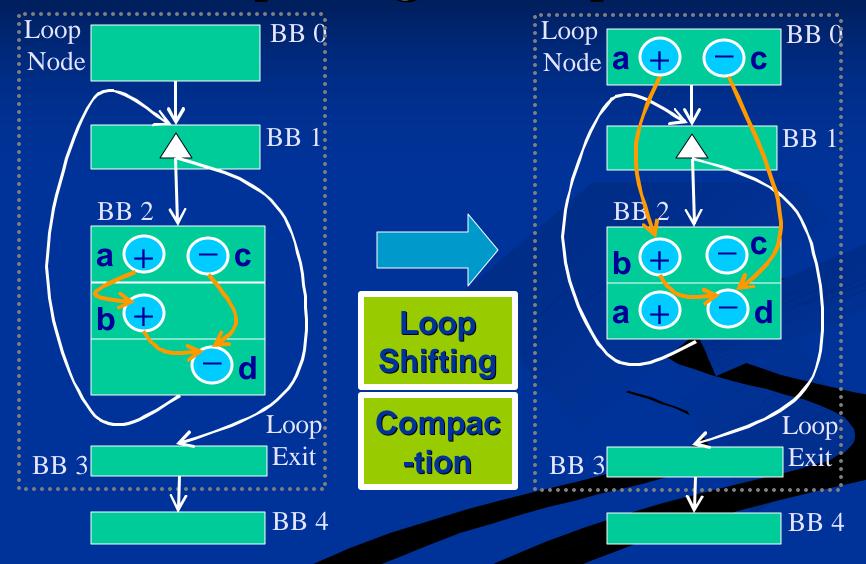

### Loop Shifting: An Incremental Loop Pipelining Technique

### Loop Shifting: An Incremental Loop Pipelining Technique

SPARK High Level Synthesis Framework

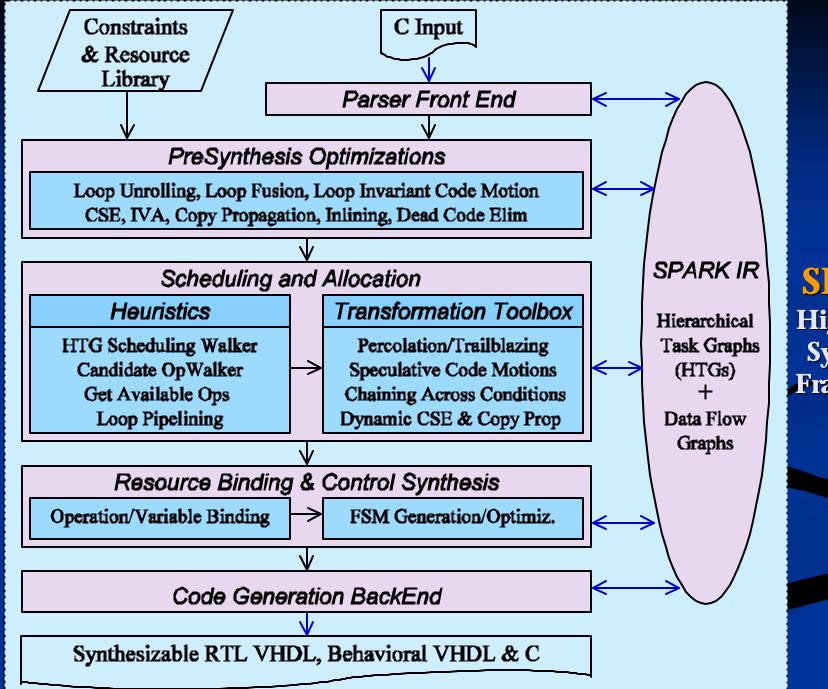

## **SPARK Parallelizing HLS Framework**

- C input and Synthesizable RTL VHDL output

- **Tool-box** of Transformations and Heuristics

- Each of these can be developed independently of the other

Script based control over transformations & heuristics

- Hierarchical Intermediate Representation (HTGs)

- Retains structural information about design (conditional blocks, loops)

- Enables efficient and structured application of transformations

- Complete HLS tool: Does Binding, Control Synthesis and Backend VHDL generation

Interconnect Minimizing Resource Binding

- Enables Graphical Visualization of Design description and intermediate results

- 100,000+ lines of C++ **code**

## **Synthesizable C**

ANSI-C front end from Edison Design Group (EDG)

Features of C not supported for synthesis

- Pointers

- However, Arrays and passing by reference are supported

- Recursive Function Calls

- Gotos

Features for which support has not been implemented

Multi-dimensional arrays

Structs

Continue, Breaks

Hardware component generated for each function

A called function is instantiated as a hardware component in calling function

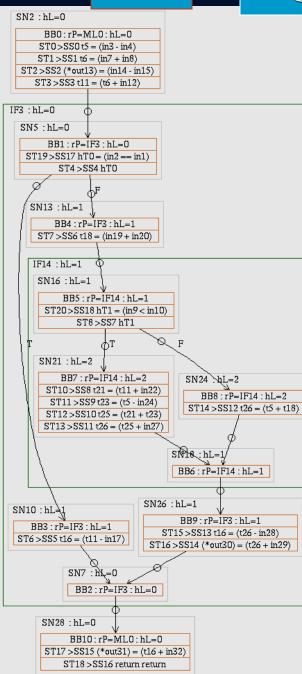

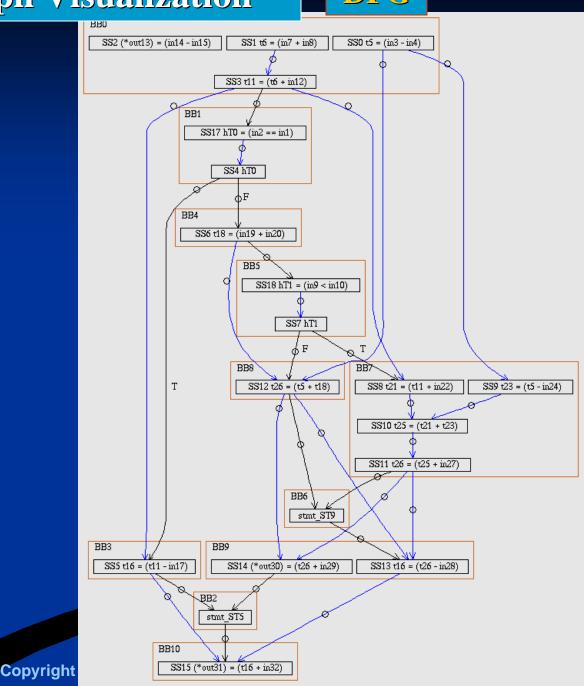

#### HTG

#### **Graph Visualization**

DFG

#### **Resource Utilization Graph**

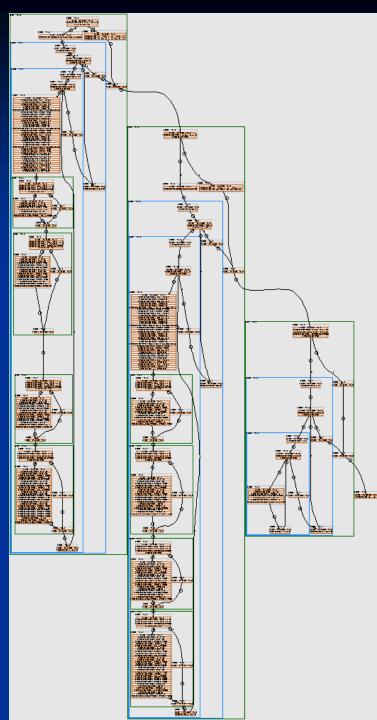

# Example of Complex HTG Example of a real design: MPEG-1 pred2 function Just for demonstration; you are not expected to read the text Multiple nested loops and conditionals

## Experiments

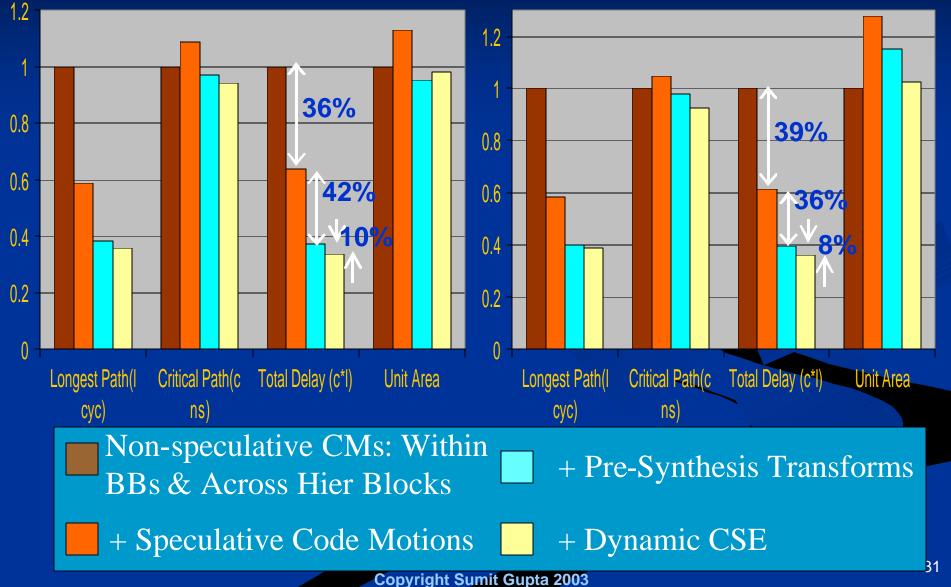

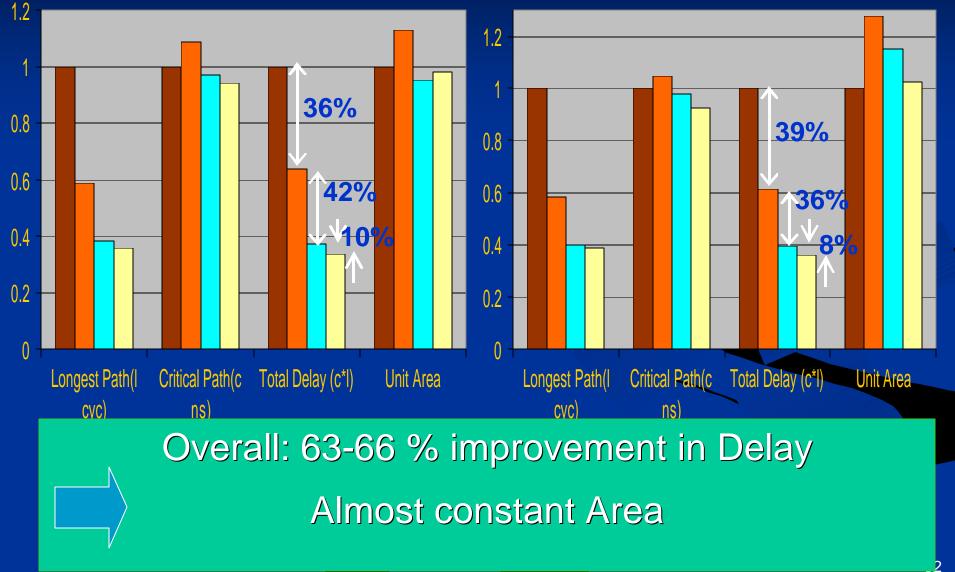

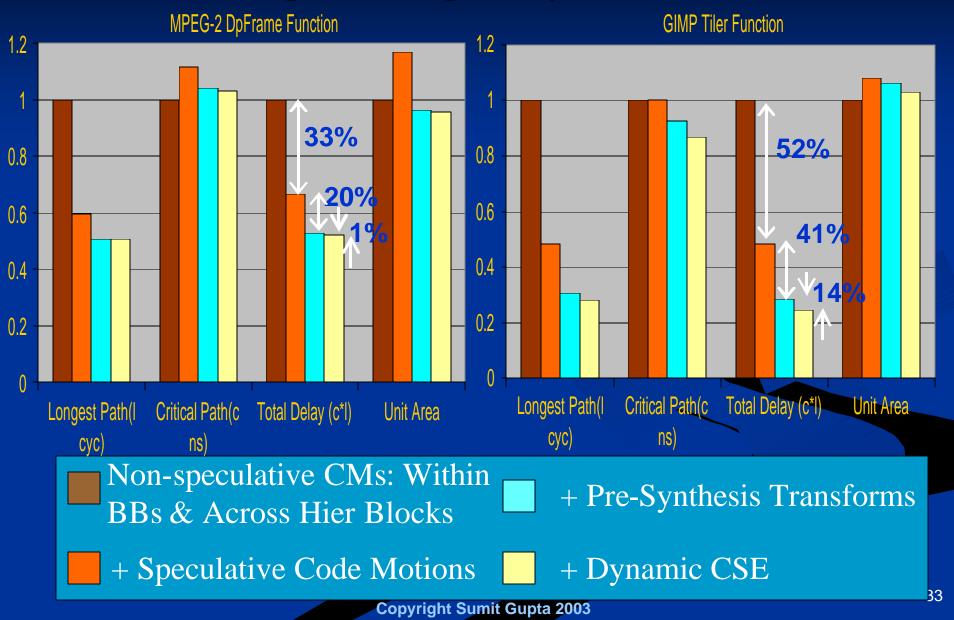

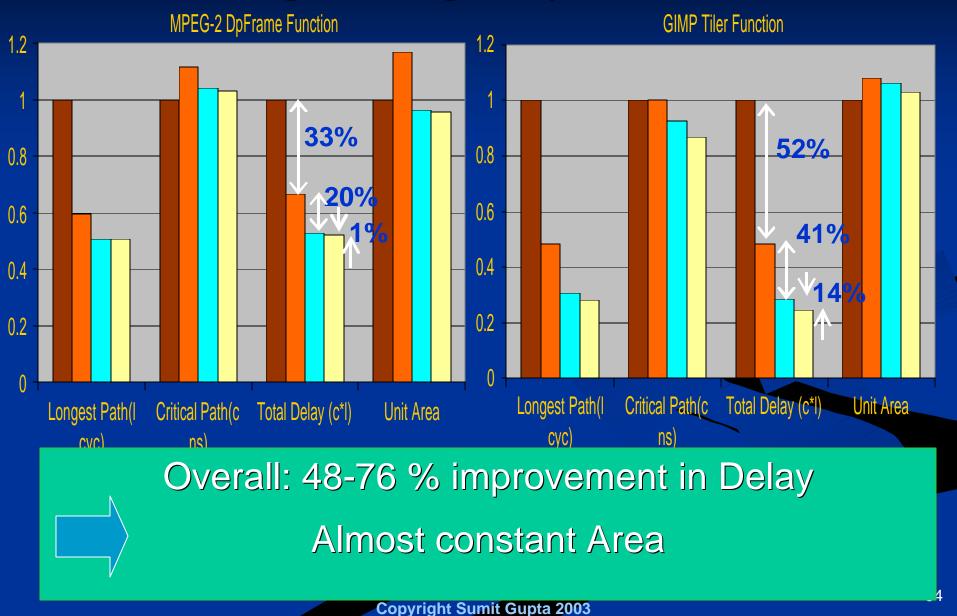

Results presented here for Pre-synthesis transformations Speculative Code Motions Dynamic CSE We used SPARK to synthesize designs derived from several industrial designs MPEG-1, MPEG-2, GIMP Image Processing software Case Study of Intel Instruction Length Decoder VHDL: Logic Synthesis Scheduling Results

Number of States in FSMCycles on Longest Path

through Design

Critical Path Length (ns)

Unit Area

## **Target Applications**

| Design   | # of Ifs | # of  | # Non-Empty  | # of       |

|----------|----------|-------|--------------|------------|

|          |          | Loops | Basic Blocks | Operations |

| MPEG-1   | 4        | 2     | 17           | 123        |

| pred1    |          |       |              |            |

| MPEG-1   | 11       | 6     | 45           | 287        |

| pred2    |          |       |              |            |

| MPEG-2   | 18       | 4     | 61           | 260        |

| dp_frame |          |       |              |            |

| GIMP     | 11       | 2     | 35           | 150        |

| tiler    |          |       |              |            |

#### MPEG-1 Pred1 Function

MPEG-1 Pred2 Function

#### MPEG-1 Pred1 Function

MPEG-1 Pred2 Function

Copyright Sumit Gupta 2003

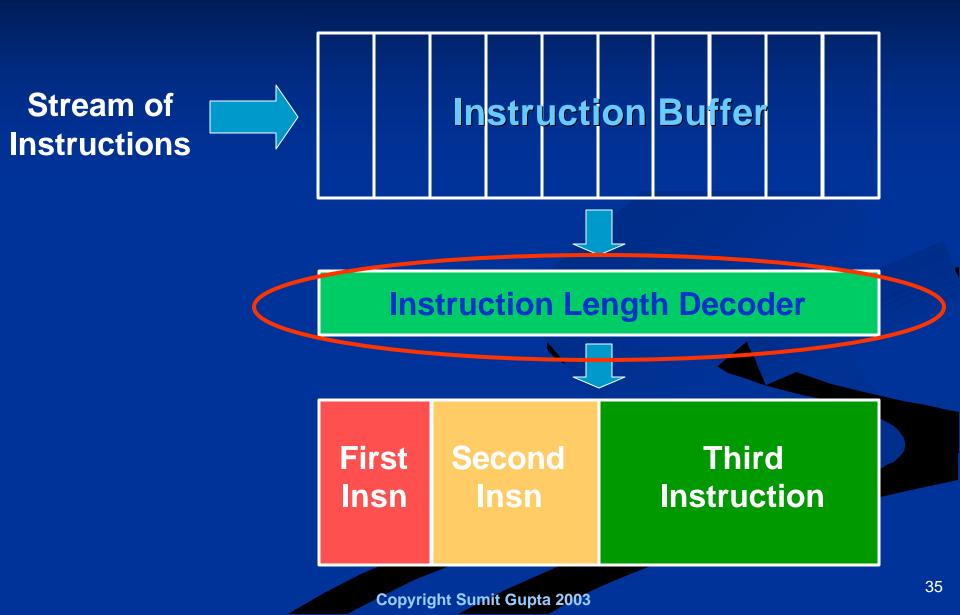

### **Case Study: Intel Instruction Length Decoder**

### **Example Design: ILD Block from Intel**

Case Study: A design derived from the Instruction Length Decoder of the Intel Pentium<sup>®</sup> class of processors

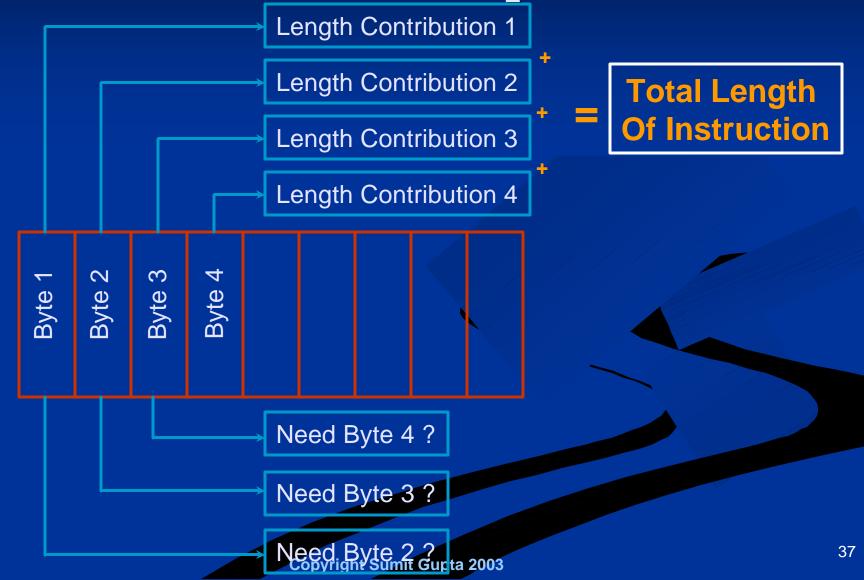

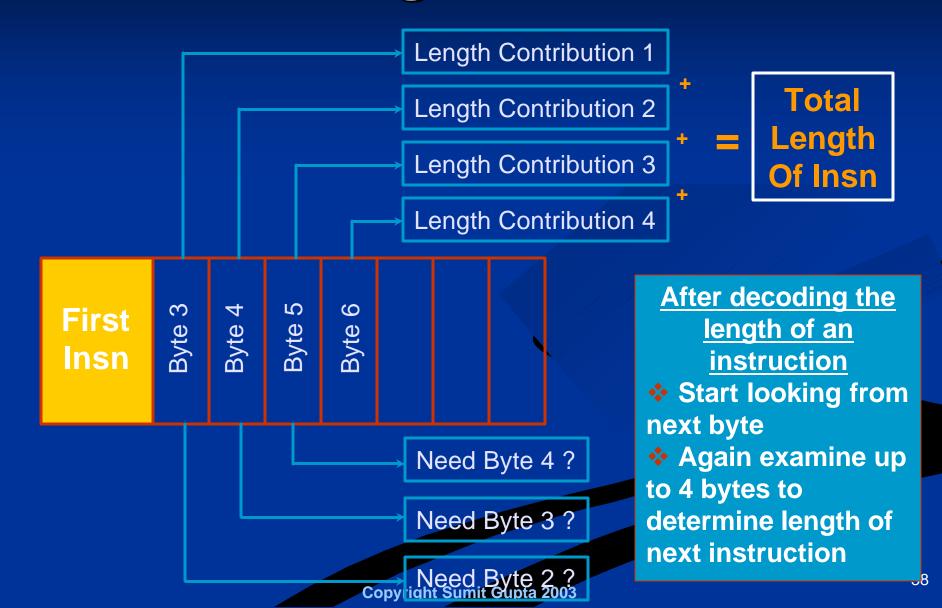

Decodes length of instructions streaming from memory

■ Has to look at up to 4 bytes at a time

Has to execute in one cycle and decode about 64 bytes of instructions

Characteristics of Microprocessor functional blocks

Low Latency: Single or Dual cycle implementation

Consist of several small computations

Intermix of control and data logic

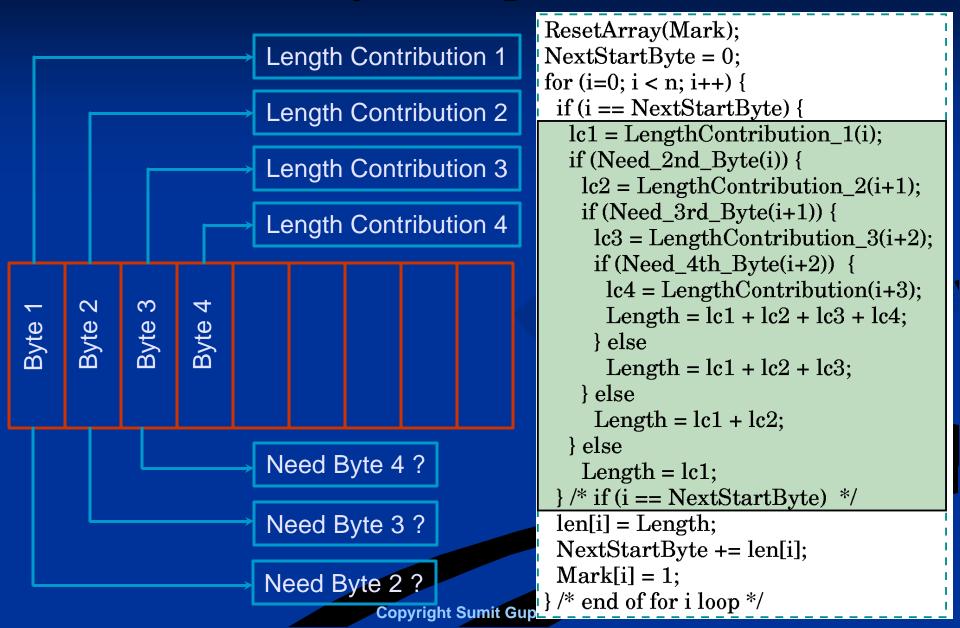

## Basic Instruction Length Decoder: Initial Description

## **Instruction Length Decoder: Decoding 2<sup>nd</sup> Instruction**

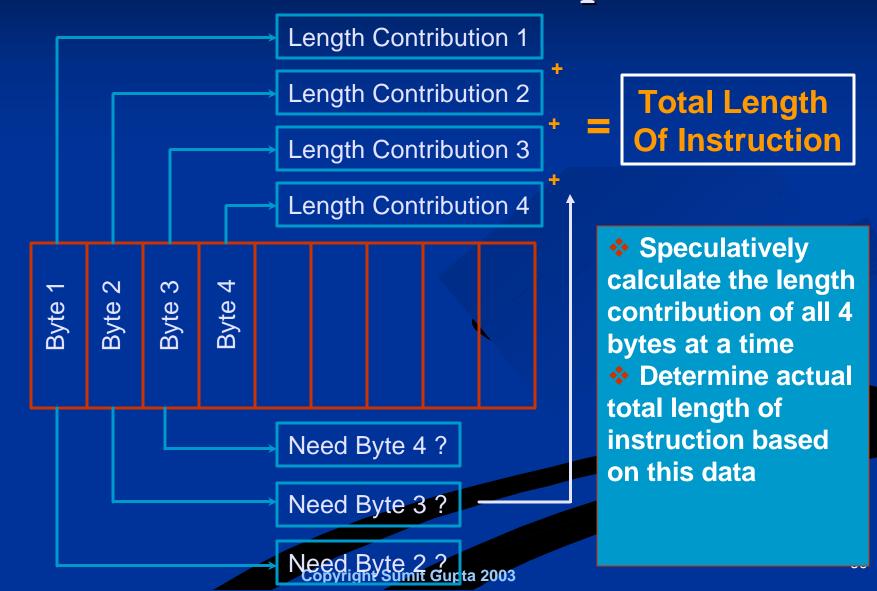

### Instruction Length Decoder: Parallelized Description

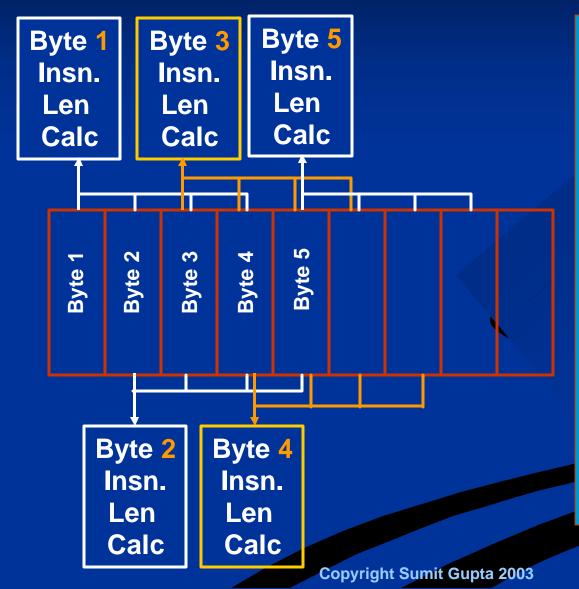

## **ILD: Extracting Further Parallelism**

Speculatively calculate length of instructions assuming a new instruction starts at each byte Do this calculation for all bytes in parallel Traverse from 1<sup>st</sup> byte to last Determine length of instructions starting from the 1<sup>st</sup> till the last Discard unused calculations

### **Initial: Multi-Cycle Sequential Architecture**

## **ILD Synthesis: Resulting Architecture**

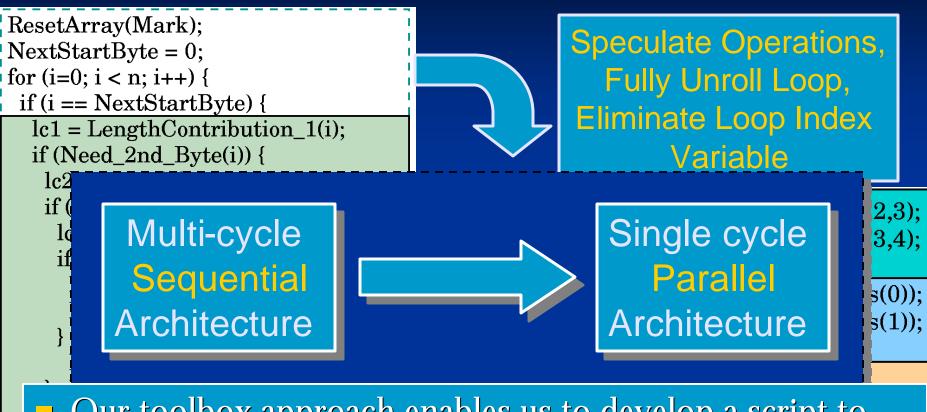

ResetArray(Mark); NextStartByte = 0; for (i=0; i < n; i++) { if (i == NextStartByte) { lc1 = LengthContribution\_1(i); if (Need\_2nd\_Byte(i)) { lc2 = LengthContribution\_2(i+1); if (Need\_3rd\_Byte(i+1)) { lc3 = LengthContribution\_3(i+2); if (Need\_4th\_Byte(i+2)) { lc4 = LengthContribution(i+3); Length = lc1 + lc2 + lc3 + lc4; } else Length = lc1 + lc2 + lc3; } else Length = lc1 + lc2; } else Length = lc1; } /\* if (i == NextStartByte) \*/ len[i] = Length; NextStartByte += len[i]; Mark[i] = 1;} /\* end of for i loop \*/

Speculate Operations, Fully Unroll Loop, Eliminate Loop Index Variable

Results(0) = DataCalculation(0,1,2,3); Results(1) = DataCalculation(1,2,3,4);

Length(0) = ControlLogic(Results(0)); Length(1) = ControlLogic(Results(1));

```

if (0 == NextStartByte) {

NextStartByte += length[0];

Mark[0] = 1;

```

```

if (1 == NextStartByte) {

NextStartByte += length[1];

Mark[1] = 1;

```

## **ILD Synthesis: Resulting Architecture**

Our toolbox approach enables us to develop a script to synthesize applications from different domains

Final design looks close to the actual implementation done by Intel

## Conclusions

Parallelizing code transformations enable a new range of HLS transformations

Provide the needed improvement in quality of HLS results

Possible to be competitive against manually designed circuits.

Can enable productivity improvements in microelectronic design

Built a synthesis system with a range of code transformations

- Platform for applying Coarse and Fine-grain Optimizations

- Tool-box approach where transformations and heuristics can be developed

- Enables the designer to find the right synthesis script for different application domains

- Performance improvements of 60-70 % across a number of designs

- We have shown its effectiveness on an Intel design

## Acknowledgements

### Advisors

Professors Rajesh Gupta, Nikil Dutt, Alex Nicolau Contributors to SPARK framework Nick Savoiu, Mehrdad Reshadi, Sunwoo Kim Intel Strategic CAD Labs (SCL) Timothy Kam, Mike Kishinevsky Supported by Semiconductor Research **Corporation and Intel SCL**

### Thank You